Memory interface latency – Achronix Speedster22i DDR User Manual

Page 30

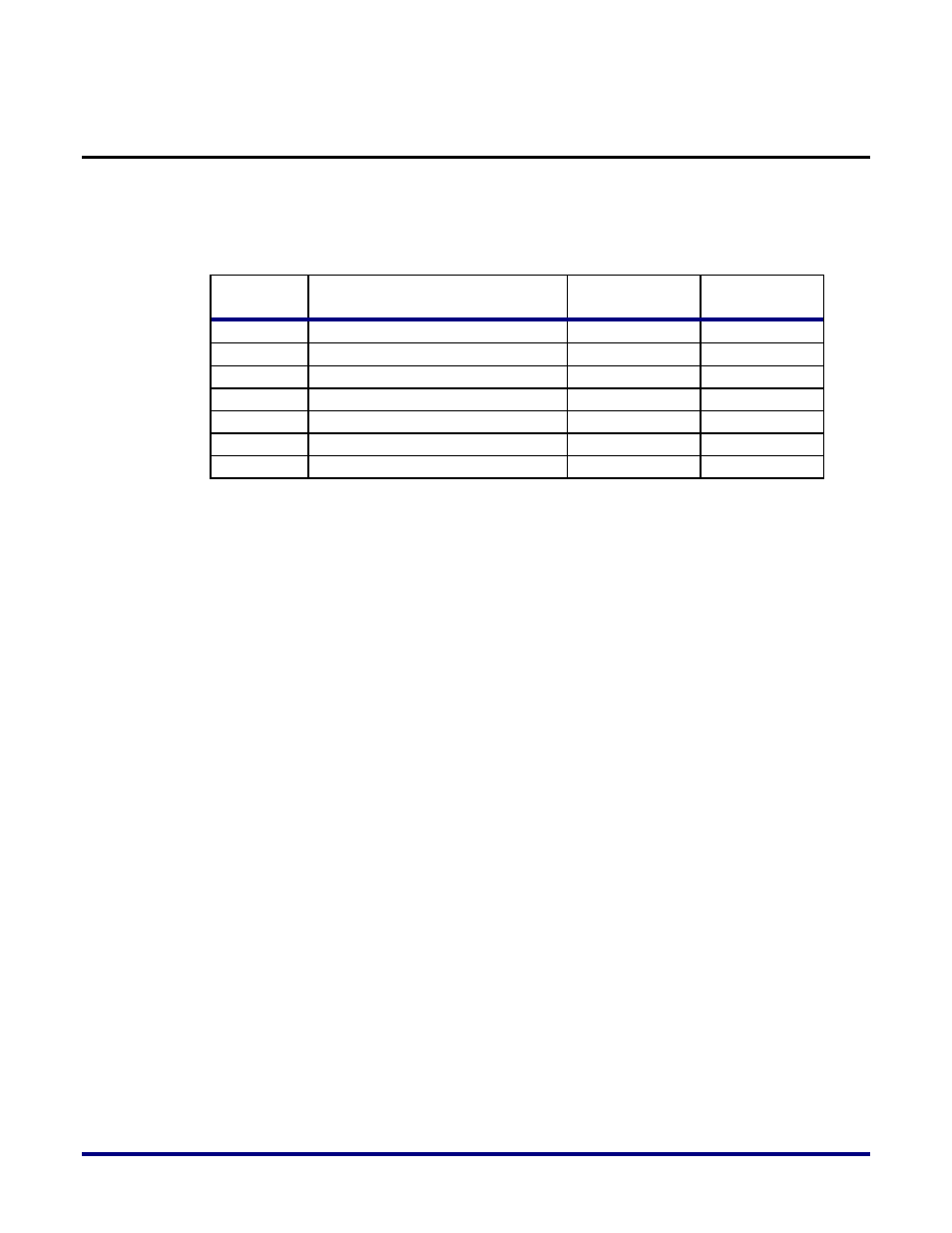

Memory Interface Latency

Depending on the data rate and the mode (width) used, the write and read latency for the

DDR3 controller will vary. Table 4 below provides detailed clock cycle counts for write and

read latencies for each of these cases.

Mode

Data-Rate

Write-Latency

(Clock Cycles)

Read-Latency

(Clock Cycles)

1X

Up to 1066 Mbps

6

8

2X

Up to 1600 Mbps

6

9

2X

From 1601 Mbps to 1866 Mbps

7

10

Wide-Bus

Up to 1600 Mbps

8

11

Wide-Bus

From 1601 Mbps to 1866 Mbps

9

12

Table-4: Latency Information for different memory controller modes

30

UG031, Nov 18, 2014