Address mapping, Figure 3: address mapping of ‘ddr_int_addr’ signal – Achronix Speedster22i DDR User Manual

Page 14

Address Mapping

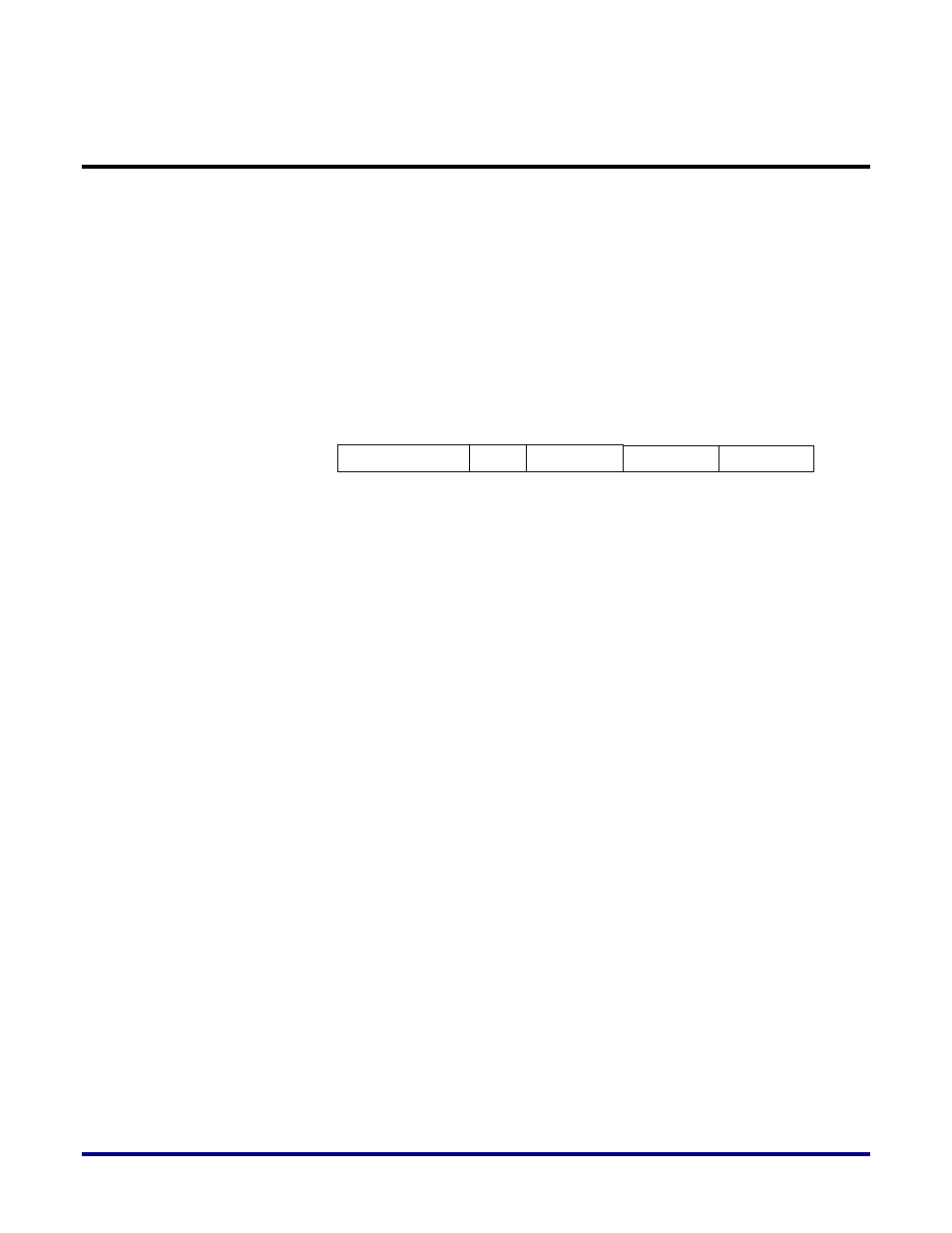

The Speedster22i DDR controller contains a specific address bus mapping which is broken

down as follows:

•

Column [colbits-1:0]

•

Bank [bankbits-1:0]

•

Row [rowbits-1:0]

•

Chip Select (encoded) [3:0]

The exact bit positions of the mapping will vary depending on the values of the configuration

parameters denoted ‘colbits,’ ‘rowbits,’ and ‘bankbits.’

Bank

Row

lsb

msb

bankbits

colbits

rowbits

ddr_int_addr[33:0]

CS[3:0]

leading 0s (if req’d)

Chip Select

Figure 3: Address mapping of ‘ddr_int_addr’ Signal

The configuration parameters relating to memory size (in terms of numbers of columns,

banks and rows) are defined by the user in the DDR Control Logic instantiation. Valid

ranges of these values are give in the “Parameters” section above.

Speedster22i devices supports four ranks per DDR control block (two dual-rank DIMM or

one quad-rank DIMM per controller). This corresponds to four chip selects: CS [3:0] = {CS3,

CS2, CS1, CS0}.

In configurations where the number of column bits, row bits, bank bits and 4 chip select bits

do not add up to the total 34 bit length of ‘ddr_int_addr ,’ the upper most bits of

‘ddr_int_addr [33:0]’ are ignored, and should be filled with zeros.

14

UG031, Nov 18, 2014