Achronix Speedster22i Interlaken User Manual

Page 39

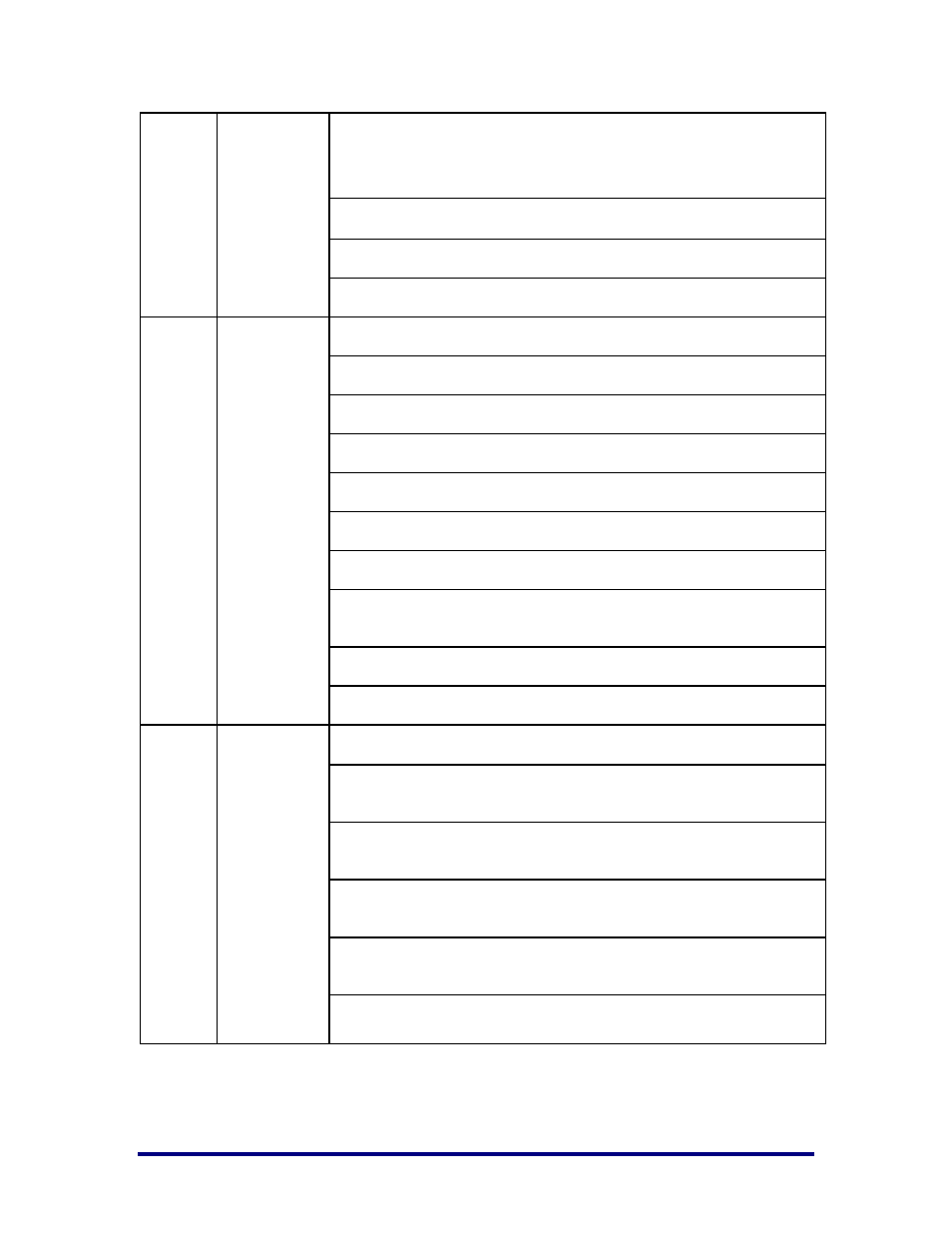

0x0210

to

0x022E

rxfcstat0-15

RX In-band Flow Control Registers (0-15) - RO

Provides the most recent value for in-band flow control for lanes 0-

255.

Register at 0x0210 – Bit 0 = Lane 0, Bit 15 = lane 15

Register at 0x0212 – Bit 0 = Lane 16, Bit 15 = lane 31

Continues Up to 0x22E where Bit 0 = lane 240 and Bit 15 = lane 255

0x0232

rxstat

RX Status Register – R/W

Bit 8 – When 1, RX CRC24 error was detected. Write 1 to clear.

Bit 7 – When 1, RX Burst error was detected. Write 1 to clear.

Bit 6 – When 1, RX BurstMax error was detected. Write 1 to clear.

Bit 5 – When 1, Missing RX Overflow was detected. Write 1 to clear.

Bit 4 - When 1, Missing EOP was detected. Write 1 to clear.

Bit 3 – When 1, Missing SOP was detected. Write 1 to clear.

Bit 2 – When 1, Meta Frame Sync Word was not detected on all lanes.

Write 1 to clear.

Bit 1 – When 1, lane alignment was lost. Write 1 to clear.

Bit 0 – When 1, all lanes are aligned.

0x0800

to

0x082E

statistics

counters

RX CRC32 Valid Statistics Registers – RO

0x0800 Bit 15:0 – returns the value contained in bits 15-0 (LSB) of RX

CRC32 Valid Statistics register for lane 0

0x0802 Bit 15:0 – returns the value contained in bits 31-16 (MSB) of

RX CRC32 Valid Statistics register for lane 0

0x0804 Bit 15:0 – returns the value contained in bits 15-0 (LSB) of RX

CRC32 Valid Statistics register for lane 1

0x0806 Bit 15:0 – returns the value contained in bits 31-16 (MSB) of

RX CRC32 Valid Statistics register for lane 1

Continues for all 12 lanes (0-11) up to address 0x082E

UG032, May 15, 2014

39