Achronix Speedster22i Interlaken User Manual

Page 20

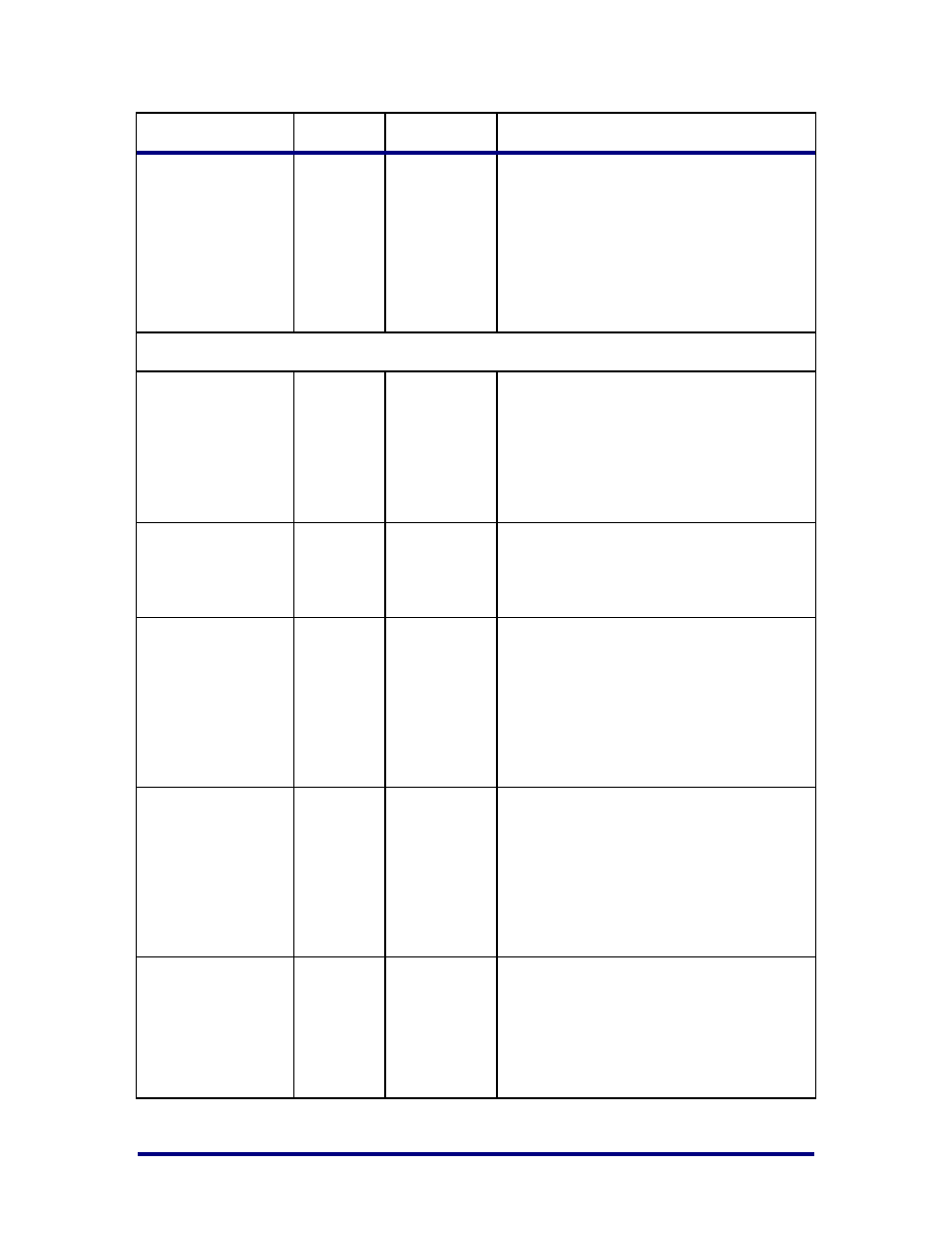

Name

Direction

Clock

Description

Words between two Control Words) was

shorter than the value specified by

ctl_tx_burstshort. This signal is only asserted

if the final Control Word did not contain an

EOP. This signal is provided to identify

poor scheduler design by the user that will

result in reduced throughput. This signal is

informational only and may be optionally

ignored.

LBUS Interface – RX Path Control/Status Signals

stat_rx_burstmax_er

r

Output

clk

RX BurstMax Error. When this signal is a

value of 1, a burst (i.e. a sequence of Data

Words between two Control Words) was

detected that was longer than the value of

ctl_tx_burstmax programmed. This signal is

informational only and may be optionally

ignored.

stat_rx_parity_err[1

2:0]

Output

clk

This bus indicates parity error in the Rx.

Bit[12] indicates parity error in the buffer

and rest all bits indicate parity error in

SerDes lane [11:0].

stat_rx_diagword_l

anestat

[11:0]

Output

clk

Lane Status messaging outputs. This bus

reflects the most recent value in bit 33 of

the Diagnostic Word received on the

respective lane. These bits should only be

considered valid if the respective bit in

stat_rx_crc32_valid is a value of 1. See

Appendix A in Interlaken Protocol

Definition rev1.2.

stat_rx_diagword_i

ntfstat

[11:0]

Output

clk

Lane Status messaging outputs. This bus

reflects the most recent value in bit 32 of

the Diagnostic Word received on the

respective lane. These bits should only be

considered valid if the respective bit in

stat_rx_crc32_valid is a value of 1. See

Appendix A in Interlaken Protocol

Definition rev1.2.

stat_rx_crc32_valid[

11:0]

Output

clk

Diagnostic Word CRC32 Valid. This bus

reflects the validity of the CRC32 in the

most recently received Diagnostic Word for

the respective lane. A value of 1 indicated

the CRC32 was valid and a value of 0

indicated the CRC32 was invalid. See

section 5.4.6 of Interlaken Protocol

UG032, May 15, 2014

20