Port list – Achronix Speedster22i Interlaken User Manual

Page 15

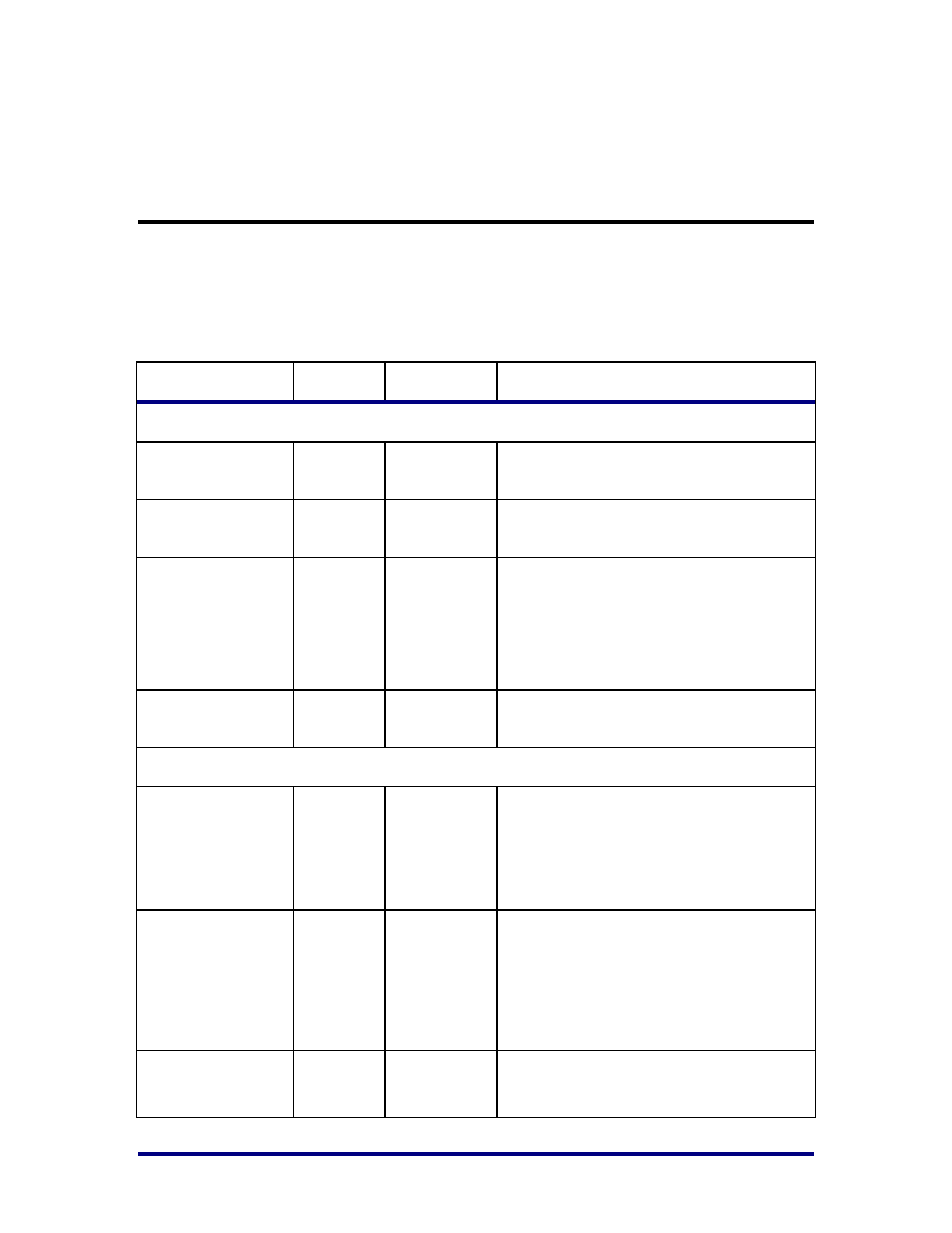

Port List

Table 1 shows the port list for the IIPC. More detail on the use of each signal is given in the

User

Interfaces

section.

Table 1 –

Port Description

Name

Direction

Clock

Description

Register Interface

sbus_req

Input

sbus_clk

Asserted for 9-cycles in case of read and for

11-cycles in case of write

sbus_datain[1:0]

Input

sbus_clk

Carries read/write indication, address and

data to write

sbus_ack

Output

sbus_clk

Acknowledgment from register i/f once

read or write is completed thru SBUS.

During write it is valid for one cycle to

indicate the end of the transfer. This is

asserted for 4-cycles to validate 8-bit data at

the end of read.

sbus_dataout[1:0]

Output

sbus_clk

Contains read data for 4-cycles when

o_sbus_ack is asserted.

Transceiver I/O

rx_serdes_data[19:0

]

Input

rx_serdes_clk

Data bus from the SerDes. There are 12

rx_serdes_data buses; one bus for each

SerDes lane and each bus has 20 bits.

By definition, bit [19] is the first bit received

by the IIPC. Bit [0] is the last bit received.

tx_serdes_data[19:0]

Output

tx_serdes_ref

clk

Data bus to the SerDes . There are 12

tx_serdes_data buses; one bus for each

SerDes lane and each bus has 20 bits.

By definition, bit [19] is the first bit

transmitted by the IIPC. Bit [0] is the last bit

transmitted.

rx_serdes_clk[11:0]

Input

Recovered clock of each SerDes lane. The

rx_serdes_data bus for each lane

synchronized to the positive edge of the

UG032, May 15, 2014

15