Achronix Speedster22i Interlaken User Manual

Page 18

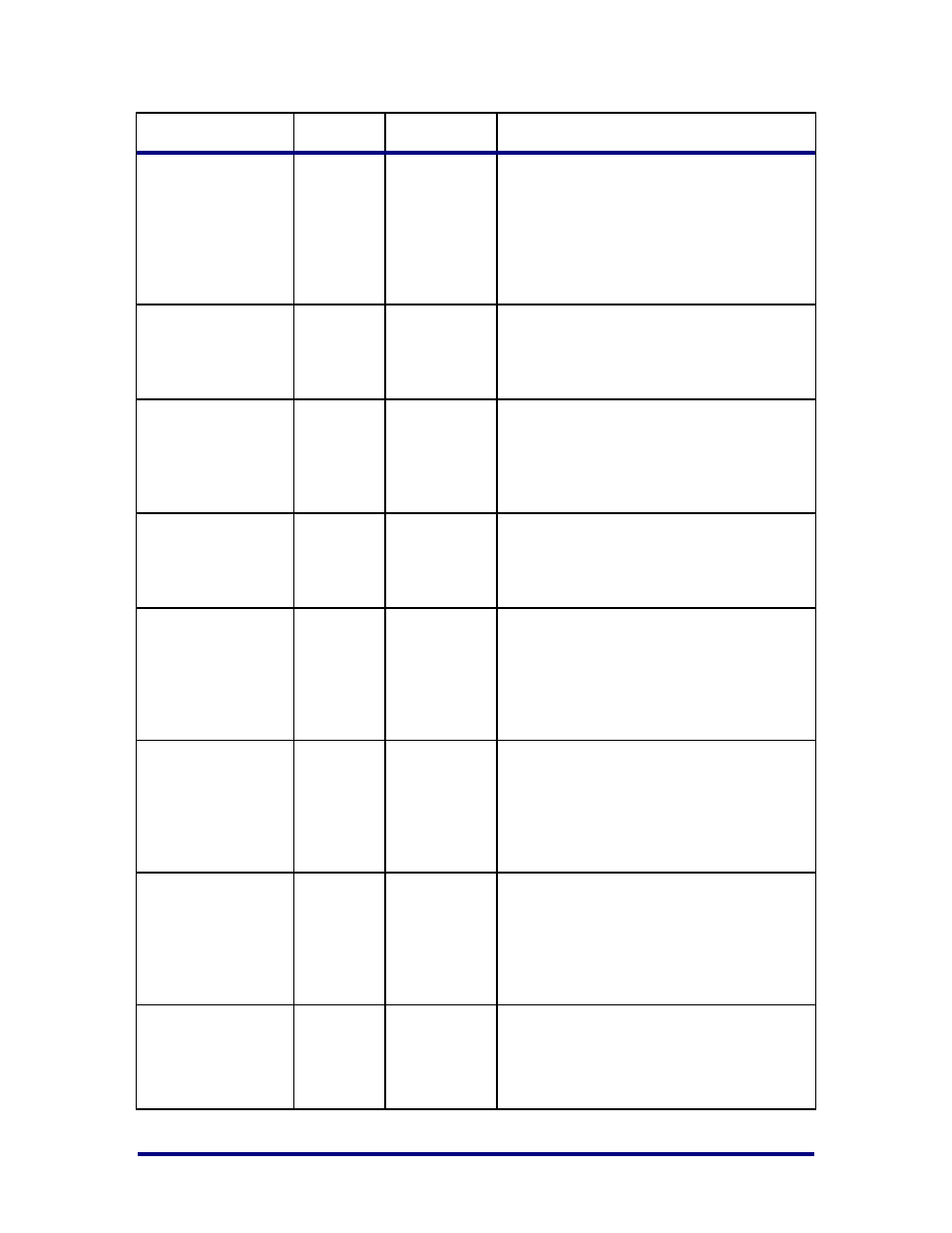

Name

Direction

Clock

Description

tx_ovfout

Output

clk

Transmit LBUS Overflow. This signal

indicates whether the user has violated the

back pressure mechanism provided by the

tx_rdyout signal. If tx_ovfout is sampled as

a 1, a violation has occurred. It is up to the

user to design the rest of the user logic in

order to not overflow the TX interface.

tx_datain[511:0]

Input

clk

Transmit LBUS Data. This bus receives

input data from the user logic. The value of

the bus is captured in every cycle that

tx_enain is sampled as 1.

tx_chanin[7:0]

Input

clk

Transmit LBUS Channel Number. This bus

receives the channel number for the packet

being written. The value of the bus is

captured in every cycle that tx_enain is

sampled as 1.

tx_enain

Input

clk

Transmit LBUS Enable. This signal is used

to enable the TX LBUS Interface. All signals

on this interface are sampled only in cycles

that tx_enain is sampled as a 1.

tx_sopin

Input

clk

Transmit LBUS Start-Of-Packet. This signal

is used to indicate the Start Of Packet (SOP)

when it is sampled as a 1 and is 0 for all

other transfers of the packet. This signal is

sampled only in cycles that tx_enain is

sampled as a 1.

tx_eopin

Input

clk

Transmit LBUS End-Of-Packet. This signal

is used to indicate the End Of Packet (EOP)

when it is sampled as a 1 and is 0 for all

other transfers of the packet. This signal is

sampled only in cycles that tx_enain is

sampled as a 1.

tx_errin

Input

clk

Transmit LBUS Error. This signal is used to

indicate a packet contains an error when it

is sampled as a 1 and is 0 for all other

transfers of the packet. This signal is

sampled only in cycles that tx_enain and

tx_eopin are sampled as 1.

tx_mtyin[5:0]

Input

clk

Transmit LBUS Empty. This bus is used to

indicate how many bytes of the tx_datain

bus are empty or invalid for the last

transfer of the current packet. This bus is

sampled only in cycles that tx_enain and

UG032, May 15, 2014

18