Rx lbus interface – Achronix Speedster22i Interlaken User Manual

Page 28

RX LBUS Interface

The synchronous RX Local bus interface provides packet oriented data much like the TX Local

bus interface accepts. All signals are synchronous with the rising-edge of the Local bus clock.

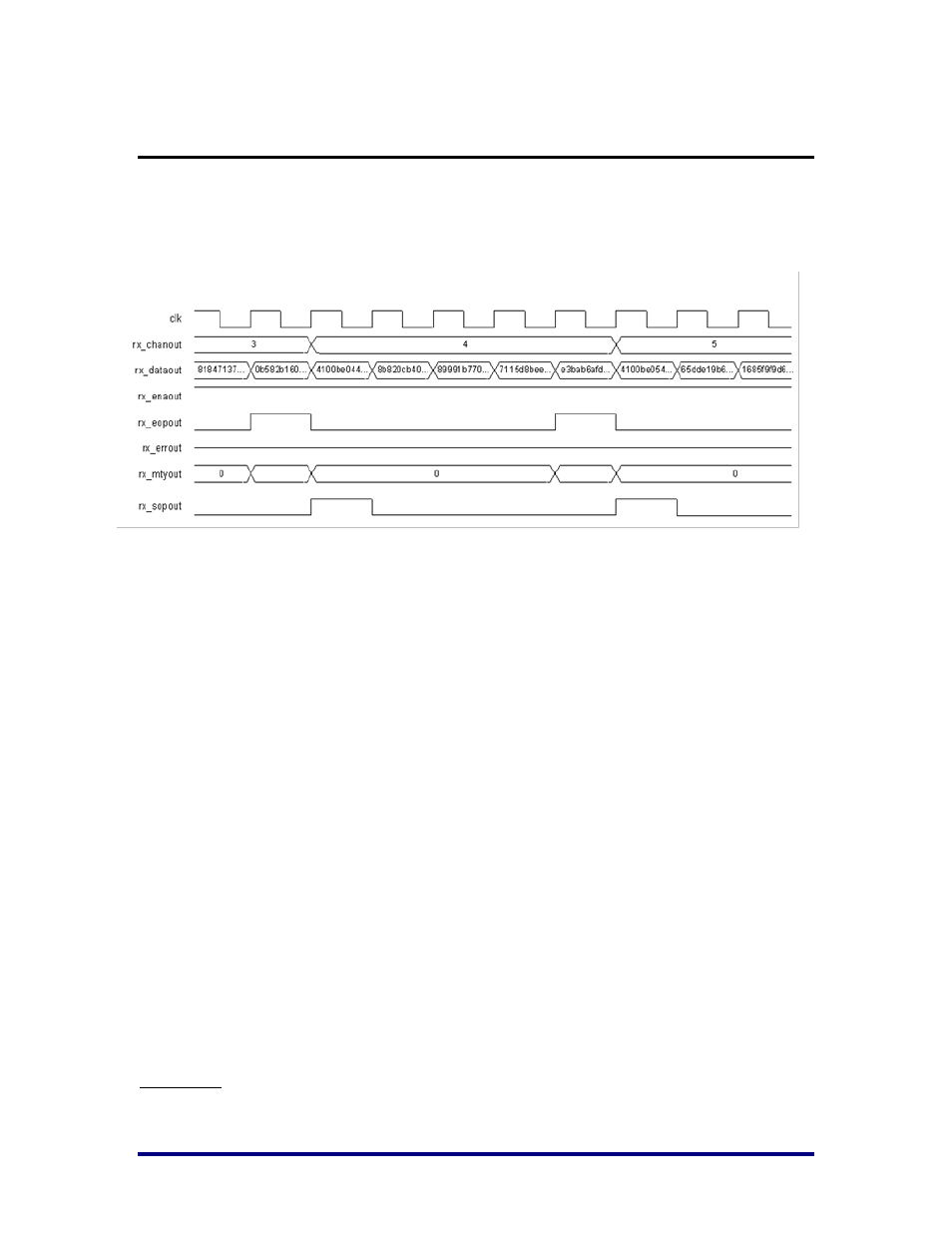

Figure 6 shows a sample waveform for data transaction for a 257 byte packet.

Figure 6: Sample RX Waveform with a 512-bit Data Bus

Data is supplied by the IIPC on every clk clock cycle when rx_enaout is asserted. This signal

qualifies the other outputs of the RX Local bus interface.

Similar to the TX Local bus interface, rx_sopout identifies the start of a packet and rx_eopout

identifies the end of a packet. Both rx_sopout and rx_eopout will be asserted during the same

cycle for packets that are less than or equal to the bus width.

The channel number for a packet is presented on the rx_chanout outputs and is valid during

every cycle rx_enaout is asserted.

Similar to the TX Local bus interface, the first byte of a packet is supplied on the most significant

bits of rx_dataout. For the 512-bit wide bus, the first byte of the packet is written on bits [511:504],

the second byte on bits [503:496], and so forth

Similar to the TX Local bus interface, portions of packets are written on the bus in the full width

of the bus unless rx_eopout is asserted. When rx_eopout is asserted, the rx_mtyout bus indicates

how many byte lanes in the data bus are invalid. The encoding is the same as for tx_mtyin.

During the last cycle of a packet, when rx_eopout is asserted with rx_enaout, rx_errout may also

be asserted. This indicates one of two things:

1. The packet was sent with the "error flag" set, or

2. An error, such as a CRC24 error, was detected sometime during the receipt of the packet.

When rx_errout is asserted the value of rx_mtyout[2:0] is always 000. The other bits of rx_mtyout

are as usual.

There is no mechanism to back pressure the RX Local bus interface.

User’s task:

63

63

UG032, May 15, 2014

28