Achronix Speedster22i Interlaken User Manual

Page 17

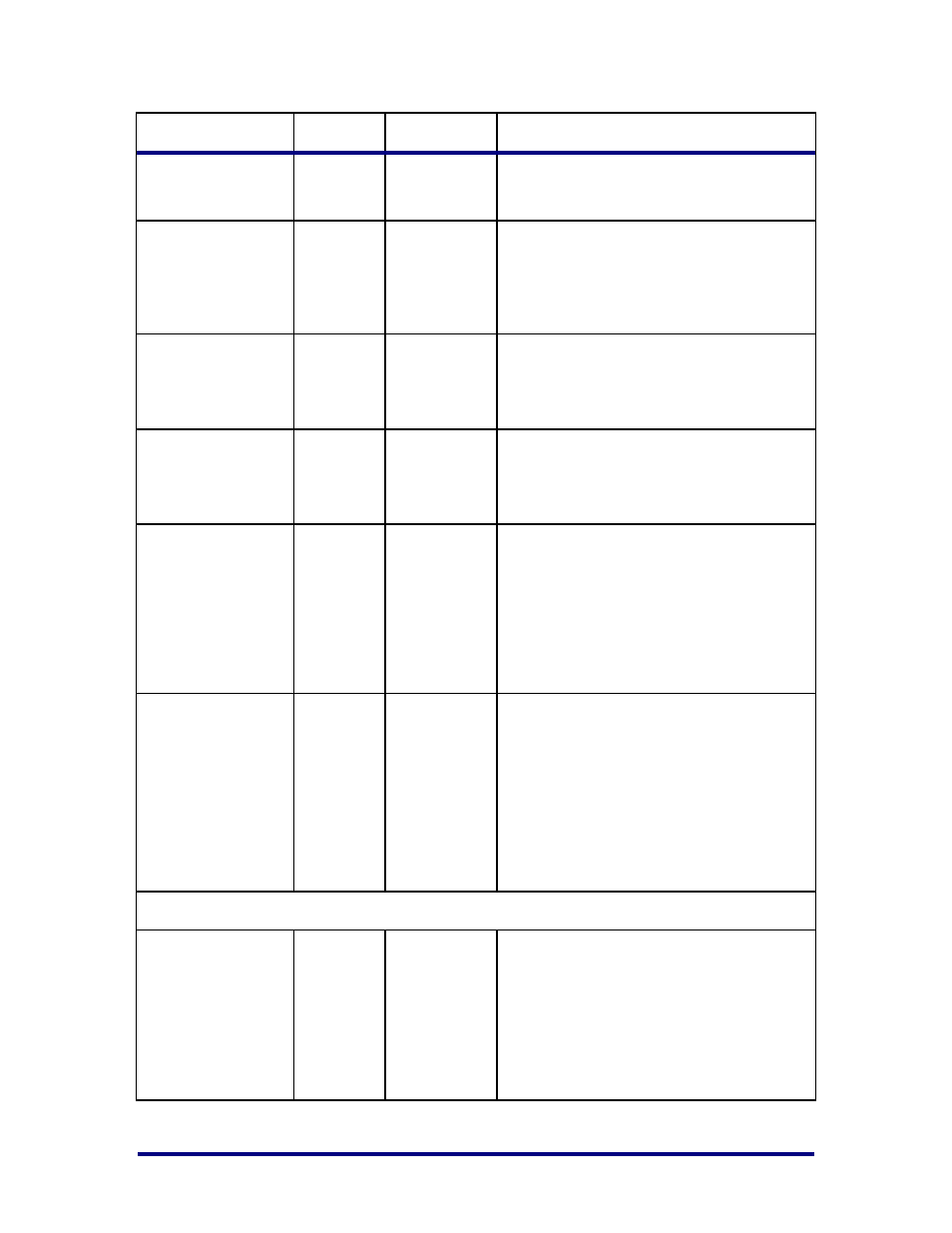

Name

Direction

Clock

Description

indicates the channel number of the in-

flight packet and is only valid in cycles that

rx_enaout is sampled as 1.

rx_enaout

Output

clk

Receive LBUS Enable. This signal qualifies

the other signal of the RX LBUS Interface.

Signals of the RX LBUS Interface are only

valid in cycles that rx_enaout is sampled as

a 1.

rx_sopout

Output

clk

Receive LBUS Start-Of-Packet. This signal

indicates the Start Of Packet (SOP) when it

is sampled as a 1 and is only valid in cycles

that rx_enaout is sampled as a 1.

rx_eopout

Output

clk

Receive LBUS End-Of-Packet. This signal

indicates the End Of Packet (EOP) when it

is sampled as a 1 and is only valid in cycles

that rx_enaout is sampled as a 1.

rx_errout

Output

clk

Receive LBUS Error. This signal indicates

that the current packet being received has

an error when it is sampled as a 1. This

signal is only valid in cycles when both

rx_enaout and rx_eopout are sampled as a

1. When this signal is a value of 0, it

indicates that there is no error in the packet

being received.

rx_mtyout[5:0]

Output

clk

Receive LBUS Empty. This bus indicates

how many bytes of the rx_dataout bus are

empty or invalid for the last transfer of the

current packet. This bus is only valid in

cycles when both rx_enaout and rx_eopout

are sampled as 1.

When rx_errout and rx_enaout are sampled

as 1, the value of rx_mtyout[2:0] is always

000. Other bits of rx_mtyout are as usual.

LBUS Interface – TX Path Signals

tx_rdyout

Output

clk

Transmit LBUS Ready. This signal indicates

whether the IIPC TX path is ready to accept

data and provides back-pressure to the user

logic. A value of 1 means the user logic can

pass data to the IIPC. A value of 0 means

the user logic must stop transferring data to

the IIPC. tx_rdyout is de-asserted when last

16-locations are available in the FIFO.

UG032, May 15, 2014

17