Jtag boundary scan signal ordering, Table u. jtag boundary scan signal ordering – Cirrus Logic EP7311 User Manual

Page 35

DS506F2

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

35

EP7311

High-Performance, Low-Power System on Chip

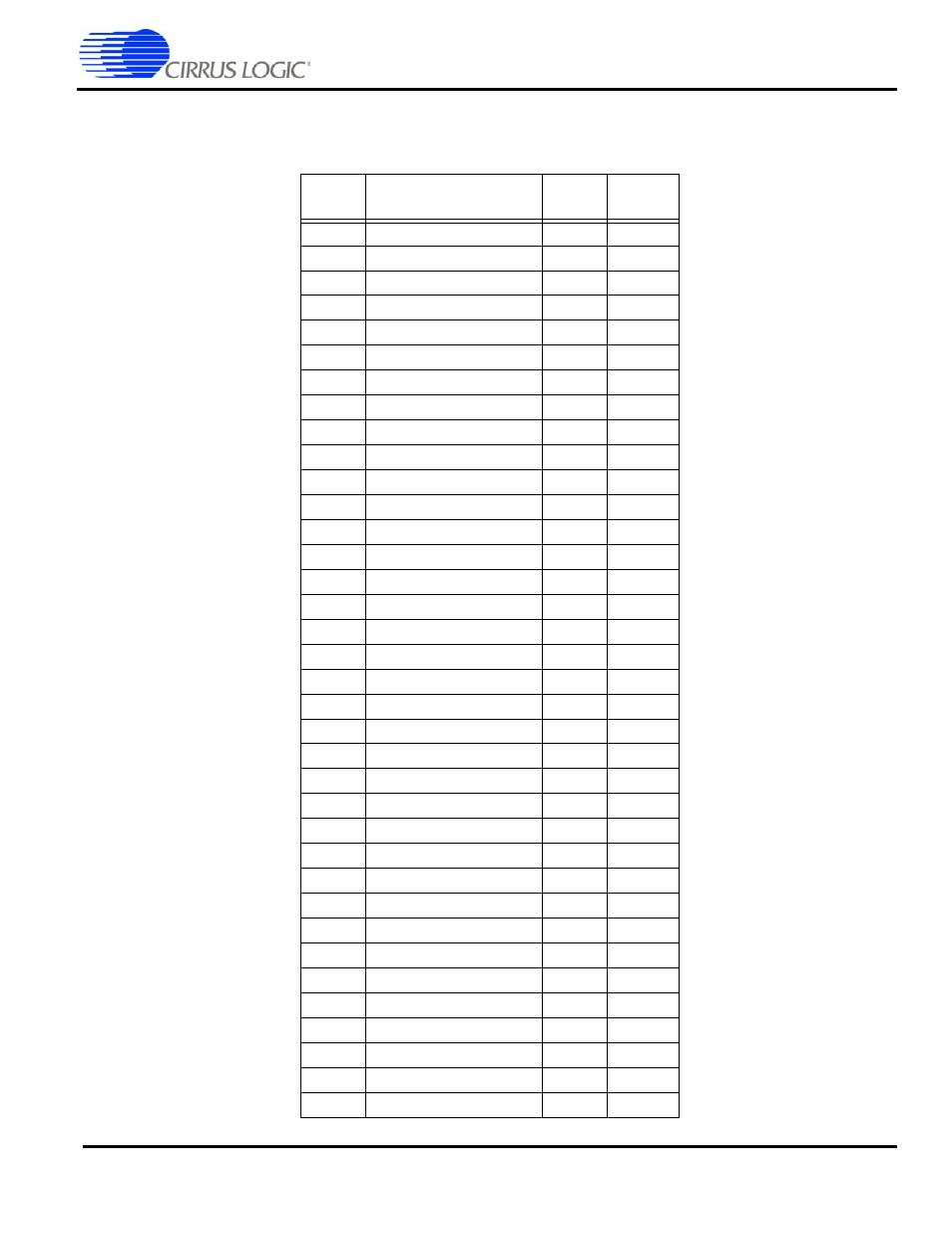

JTAG Boundary Scan Signal Ordering

Table U. JTAG Boundary Scan Signal Ordering

PBGA

Ball

Signal

Type

Position

B1

nCS[5]

O

1

C2

EXPCLK

I/O

3

E4

WORD

O

6

D1

WRITE/nSDRAS

O

8

F5

RUN/CLKEN

O

10

D2

EXPRDY

I

13

F4

TXD2

O

14

E1

RXD2

I

16

E2

PB[7]

I/O

17

G5

PB[6]

I/O

20

F1

PB[5]

I/O

23

G4

PB[4]

I/O

26

F2

PB[3]

I/O

29

H7

PB[2]

I/O

32

G1

PB[1]/PRDY2

I/O

35

H6

PB[0]/PRDY1

I/O

38

H1

PA[7]

I/O

41

H5

PA[6]

I/O

44

H2

PA[5]

I/O

47

H4

PA[4]

I/O

50

J1

PA[3]

I/O

53

J4

PA[2]

I/O

56

J2

PA[1]

I/O

59

J5

PA[0]

I/O

62

K1

LEDDRV

O

65

J6

TXD1

O

67

K2

PHDIN

I

69

J7

CTS

I

70

L1

RXD1

I

71

K4

DCD

I

72

L2

DSR

I

73

K5

nTEST1

I

74

M1

nTEST0

I

75

K6

EINT3

I

76

M2

nEINT2

I

77

L4

nEINT1

I

78

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)