Cirrus Logic EP7311 User Manual

Ep7311 data sheet, Overview block diagram features, Arm720t

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

MAR ‘11

DS506F2

High-performance,

Low-power, System-on-chip

with SDRAM & Enhanced

Digital Audio Interface

EP7311 Data Sheet

OVERVIEW

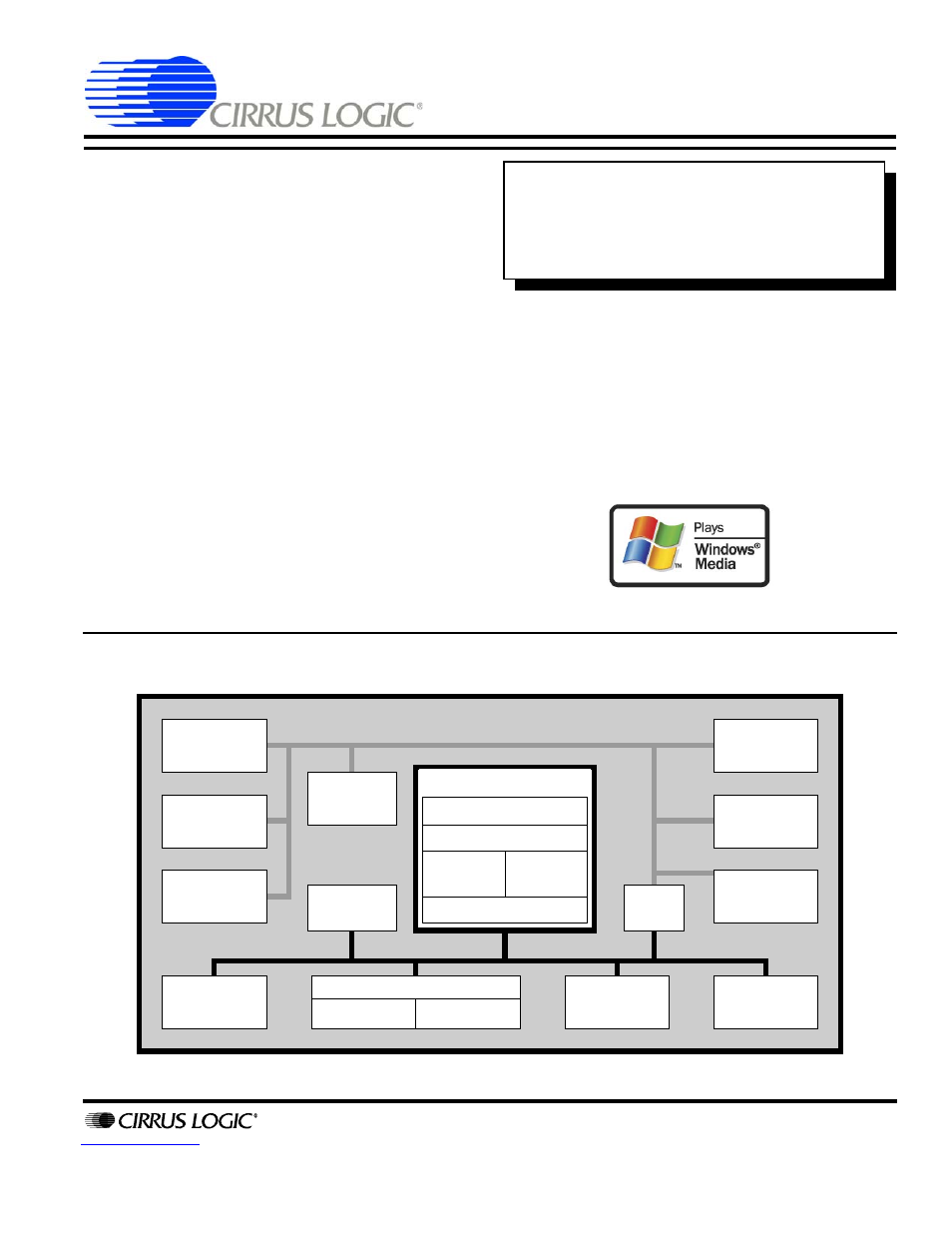

BLOCK DIAGRAM

FEATURES

(cont.)

(cont.)

ARM720T Processor

— ARM7TDMI CPU

— 8 KB of four-way set-associative cache

— MMU with 64-entry TLB

— Thumb code support enabled

Ultra low power

— 90 mW at 74 MHz typical

— 30 mW at 18 MHz typical

— 10 mW in the Idle State

— <1 mW in the Standby State

48 KB of on-chip SRAM

MaverickKey

™

IDs

— 32-bit unique ID can be used for SDMI compliance

— 128-bit random ID

Dynamically programmable clock speeds of

18, 36, 49, and 74 MHz

LCD

Controller

Boot

ROM

MaverickKey

TM

ARM7TDMI CPU Core

MMU

8 KB

Cache

Write

Buffer

Internal Data Bus

EPB Bus

Memory Controller

SDRAM I/F

SRAM I/F

On-chip SRAM

48 KB

ICE-JTAG

Clocks &

Timers

Keypad&

Touch

Screen I/F

Interrupts,

PWM & GPIO

Bus

Bridge

(2) UARTs

w/ IrDA

Power

Management

Serial

Interface

Multimedia

Codec Port

ARM720T

MEMORY AND STORAGE

U

SER INTERF

AC

E

SERIAL PORTS

The Maverick™ EP7311 is designed for ultra-low-power

applications such as PDAs, smart cellular phones, and

industrial hand held information appliances. The core-logic

functionality of the device is built around an ARM720T

processor with 8 KB of four-way set-associative unified cache

and a write buffer. Incorporated into the ARM720T is an

enhanced memory management unit (MMU) which allows for

support of sophisticated operating systems like Linux

®

.

Document Outline

- Features

- Overview

- Processor Core - ARM720T

- Power Management

- MaverickKey™ Unique ID

- Memory Interfaces

- Digital Audio Capability

- Universal Asynchronous Receiver/Transmitters (UARTs)

- Multimedia Codec Port (MCP)

- CODEC Interface

- SSI2 Interface

- Synchronous Serial Interface

- LCD Controller

- Interrupt Controller

- Real-Time Clock

- PLL and Clocking

- DC-to-DC converter interface (PWM)

- Timers

- General Purpose Input/Output (GPIO)

- Hardware debug Interface

- Internal Boot ROM

- Packaging

- Pin Multiplexing

- System Design

- Electrical Specifications

- Timings

- Packages

- Conventions

- Ordering Information

- Environmental, Manufacturing, & Handling Information

- Revision History