17 line length channel id register (10h), 18 line length data register (11h), 19 output disable register (12h) – Cirrus Logic CS61880 User Manual

Page 38: 20 ais status register (13h), Table 12. transmitter pulse shape selection, Line, Length data register (11h), See section 14.18 on, Line length data register (11h), See section

CS61880

38

DS450PP3

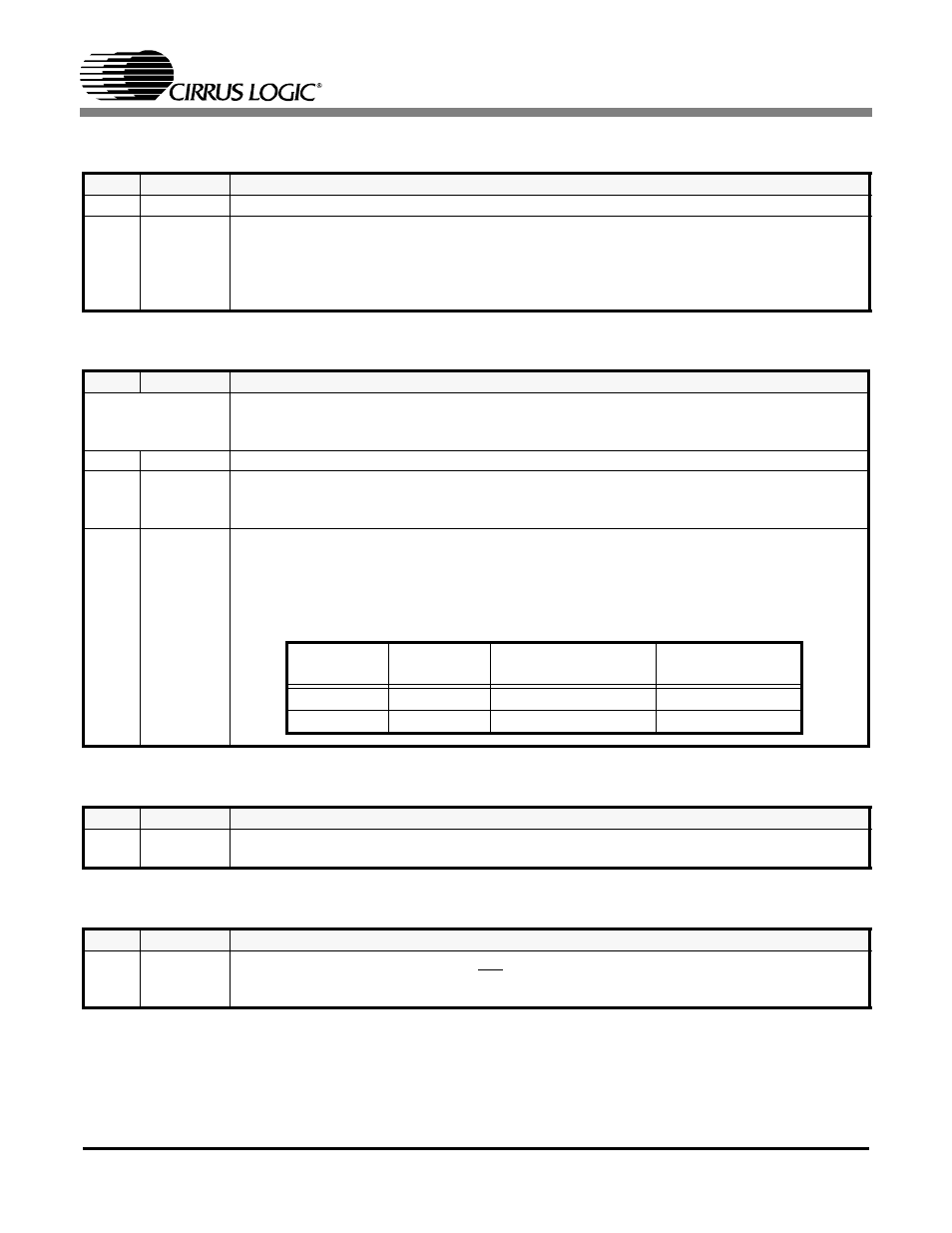

14.17 Line Length Channel ID Register (10h)

14.18 Line Length Data Register (11h)

14.19 Output Disable Register (12h)

14.20 AIS Status Register (13h)

BIT

NAME

Description

[7:3]

RSVD 7-3

RESERVED (These bits must be set to 0.)

[2:0]

LLID 2-0

The value written to these bits specify the LIU channel for which the Pulse Shape Configura-

tion Data (register 11h) applies. For example, writing a value of a binary 000 to the 3-LSBs

will select channel 0. The pulse shape configuration data for the channel specified in this reg-

ister are written or read through the Line Length Data Register (11h). Register bits default

to 00h after power-up or reset.

BIT

NAME

Description

The value written to the 4-LSBs of this register specifies whether the device is operating in

either E1 75

Ω

or E1 120

Ω

mode and the associated pulse shape as shown below is being

transmitted. Register bits default to 00h after power-up or reset.

[7:5]

RSVD

RESERVED (These bits must be set to 0.)

[4]

INT_EXTB

This bit specifies the use of internal (Int_ExtB = 1) or external (Int_ExtB = 0) receiver line

matching. The line impedance for both the receiver and transmitter are chosen through the

LEN [3:0] bits in this register.

[3:0]

LEN[3:0]

These bits set the line impedance for both the receiver and the transmitter path and the

desired pulse shape for a specific channel. The channel is selected with the Line Length

Channel ID register (0x10). The following table shows the available transmitter pulse

shapes.

BIT

NAME

Description

[7:0]

OENB 7-0 Setting bit n of this register to “1” High-Z the TX output driver on channel n of the device.

Register bits default to 00h after power-up or reset.

BIT

NAME

Description

[7:0]

AISS 7-0

A “1” in bit position n indicates that the receiver has detected an AIS condition on channel n,

which generates an interrupt on the INT pin. Register bits default to 00h after power-up or

reset.

Table 12. Transmitter Pulse Shape Selection

LEN [3:0]

Operation

Mode

Line Length

Selection

Phase Samples

per UI

0000

E1

120

Ω

3.0 V

12

1000

E1

75

Ω

2.37 V

12