Building, Integrated timing systems (bits) clock mode, T1 1:2 – Cirrus Logic CS61880 User Manual

Page 23

CS61880

DS450PP3

23

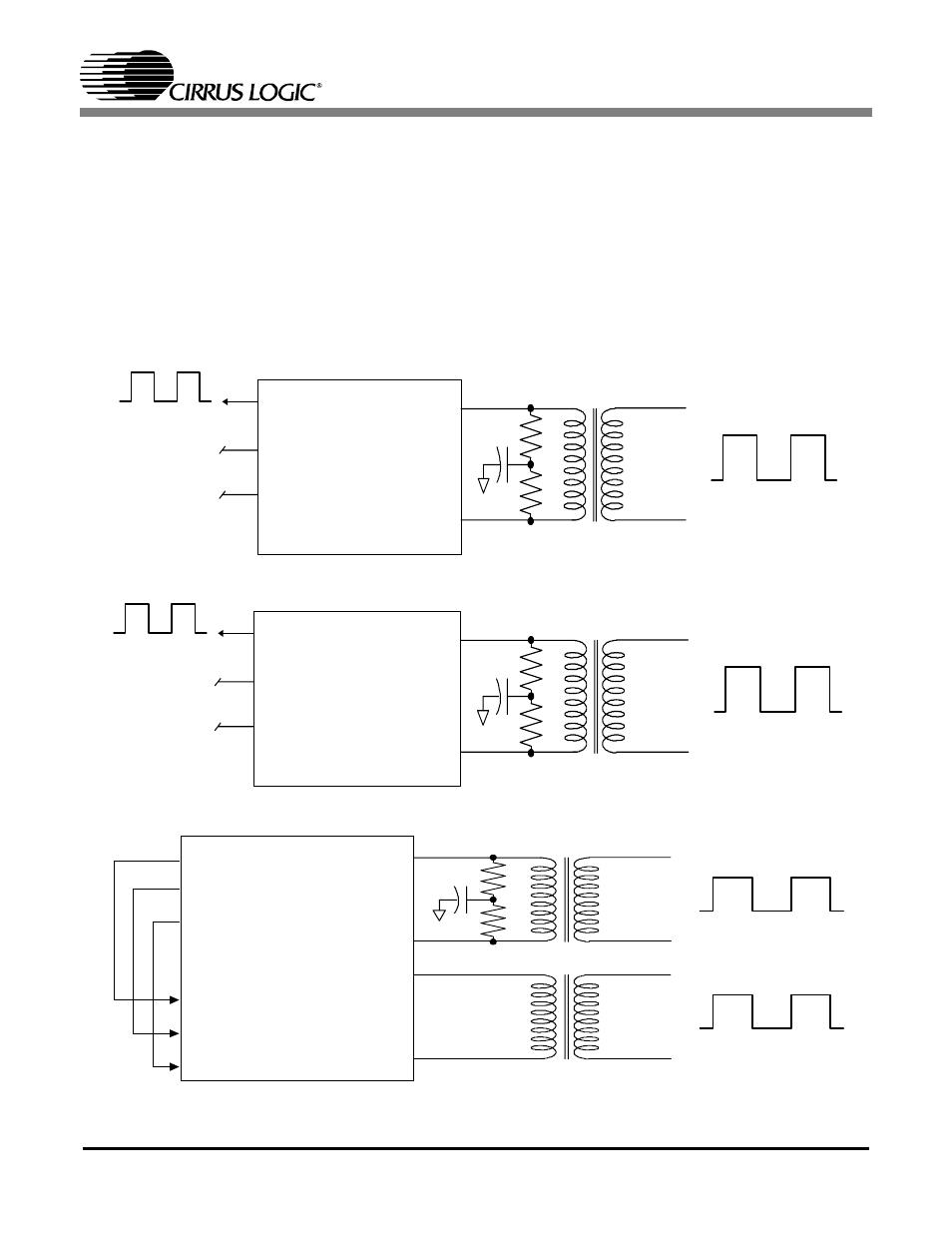

8. BUILDING INTEGRATED TIMING SYSTEMS (BITS) CLOCK MODE

This mode is used to enable one or more channels

as a stand-alone timing recovery unit used for

G.703 Clock Recovery.

In hardware mode, BITS Clock mode is selected by

pulling the MUX pin “HIGH”. This enables only

channel zero as a stand-alone timing recovery unit,

no other channel can be used as a timing recovery

unit.

In host mode, each channel can be setup as an inde-

pendent G.703 timing recovery unit, through the

Bits Clock Enable Register (1Eh)

14.31 on page 40), setting the desired bit to “1” en-

ables BITS Clock mode for that channel. The fol-

lowing diagrams show how the BITS clock

function operates.

T1 1:2

RRING

R1

R2

RECEIVE

LINE

0.1

µ

F

CS61880

One Receiver

RTIP

RCLK

RPOS

RNEG

Figure 3. G.703 BITS Clock Mode in NRZ Mode

T1 1:2

RRING

R1

R2

RECEIVE

LINE

0.1

µ

F

CS61880

One Receiver

RTIP

RCLK

RPOS

RNEG

Figure 4. G.703 BITS Clock Mode in RZ Mode

T1 1:2

RRING

R1

R2

RECEIVE

LINE

0.1

µ

F

CS61880

One Channel

RTIP

RCLK

RPOS

RNEG

TCLK

TPOS

TNEG

REMOTE

LOOPBACK

T1 1:1.15

TRANMIT

LINE

TRING

TTIP

Figure 5. G.703 BITS Clock Mode in Remote Loopback