8 jtag test interface, 9 miscellaneous, 8 jtag test interface 3.9 miscellaneous – Cirrus Logic CS61880 User Manual

Page 21

CS61880

DS450PP3

21

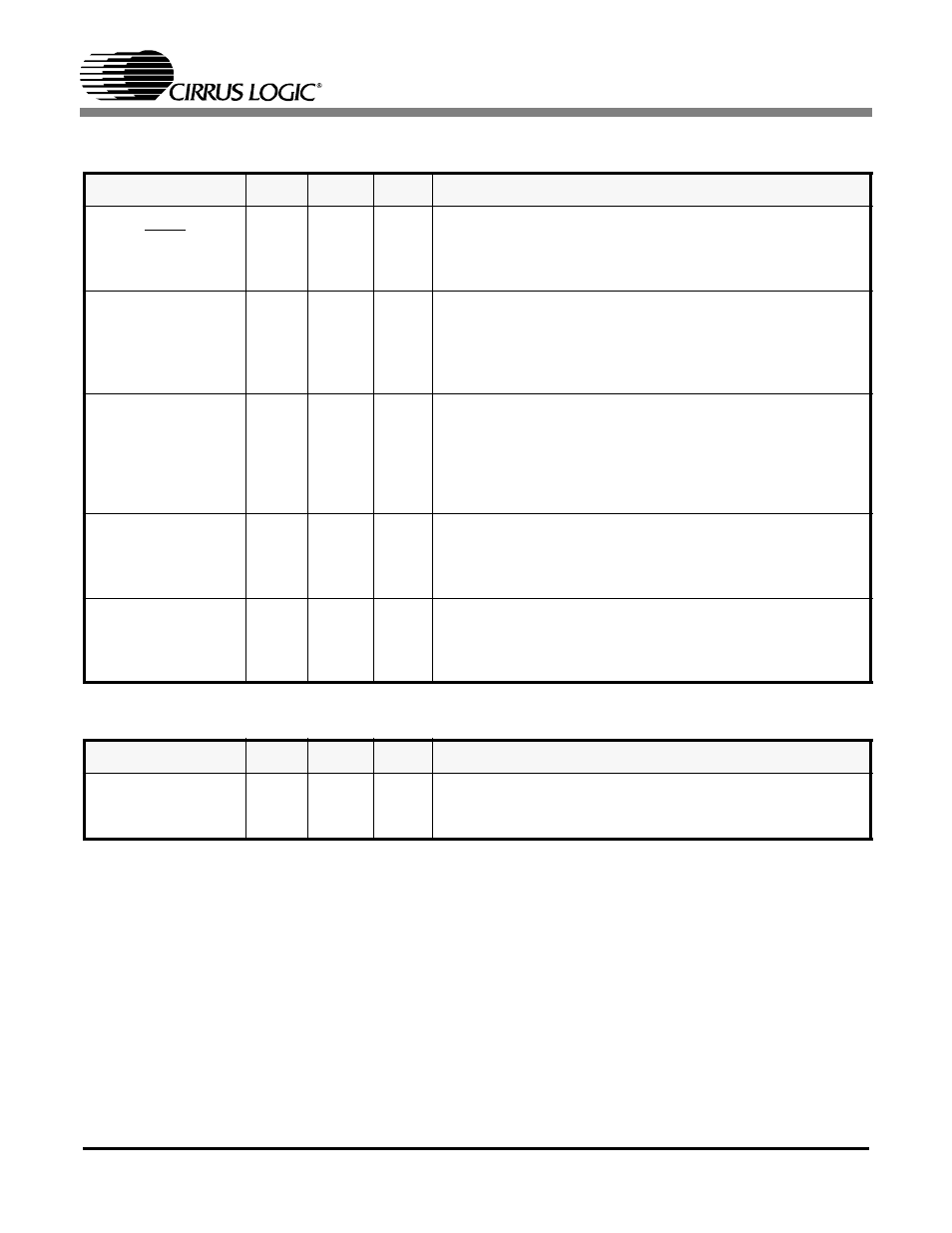

3.8 JTAG Test Interface

3.9 Miscellaneous

SYMBOL

LQFP

FBGA

TYPE

DESCRIPTION

TRST

95

G12

I

JTAG Reset

This active Low input resets the JTAG controller. This input

is pulled up internally and may be left as a NC when not

used.

TMS

96

F11

I

JTAG Test Mode Select Input

This input enables the JTAG serial port when active High.

This input is sampled on the rising edge of TCK. This input

is pulled up internally and may be left as a NC when not

used.

TCK

97

F14

I

JTAG Test Clock

Data on TDI is valid on the rising edge of TCK. Data on

TDO is valid on the falling edge of TCK. When TCK is

stopped high or low, the contents of all JTAG registers re-

main unchanged. Tie pin low through a 10 k

Ω

resistor when

not used.

TDO

98

F13

O

JTAG Test Data Output

JTAG test data is shifted out of the device on this pin. Data

is output on the falling edge of TCK. Leave as NC when not

used.

TDI

99

F12

I

JTAG Test Data Input

JTAG test data is shifted into the device using this pin. The

pin is sampled on the rising edge of TCK. TDI is pulled up

internally and may be left as a NC when not used.

SYMBOL

LQFP

FBGA

TYPE

DESCRIPTION

REF

94

H13

I

Reference Input

This pin must be tied to ground through 13.3 k

Ω

1% resis-

tor. This pin is used to set the internal current level.