7 analog rx/tx data i/o – Cirrus Logic CS61880 User Manual

Page 19

CS61880

DS450PP3

19

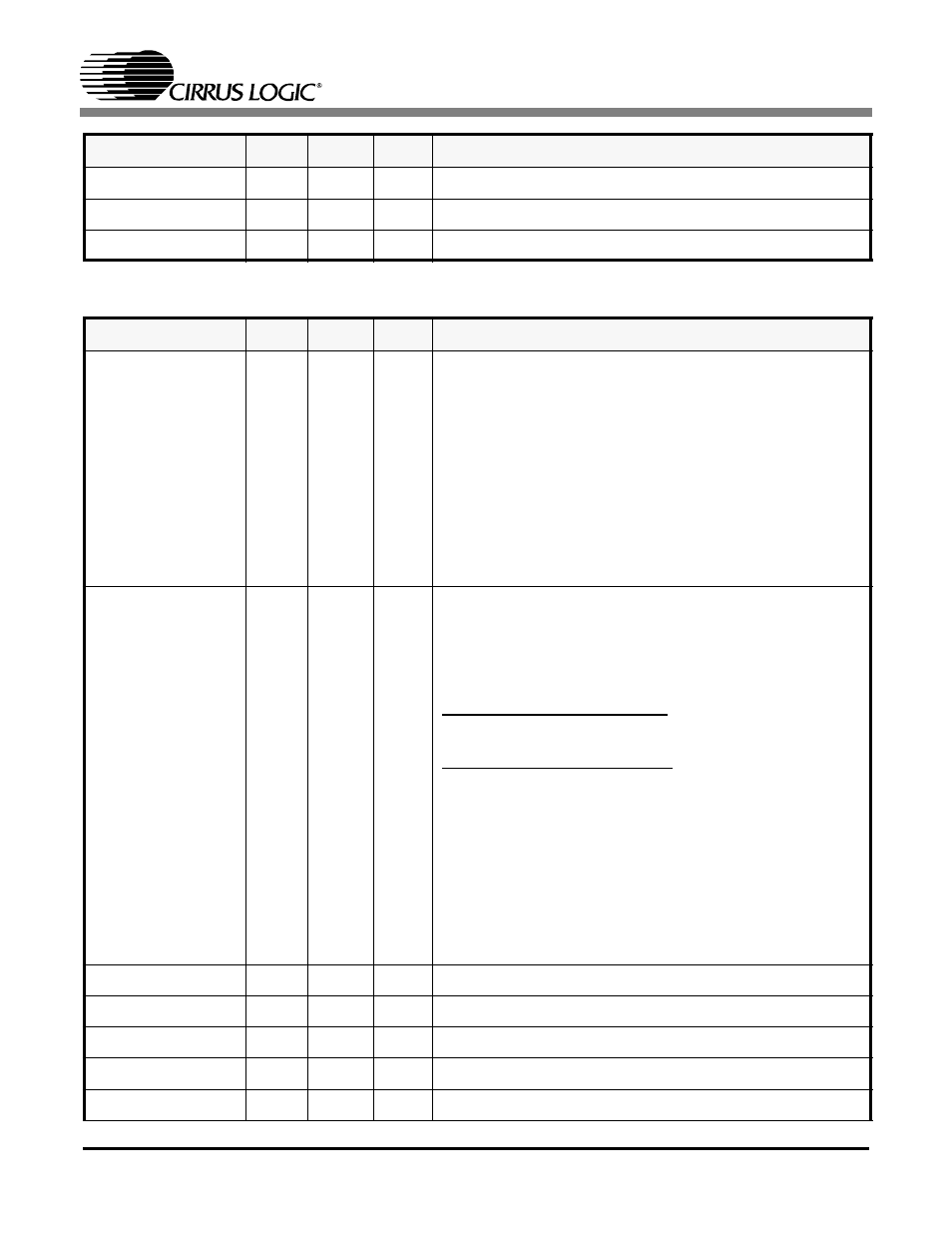

3.7 Analog RX/TX Data I/O

RCLK7

143

A1

O

Receive Clock Output Port 7

RPOS7/RDATA7

142

A2

O

Receive Positive Pulse/ Receive Data Output Port 7

RNEG7/BPV7

141

A3

O

Receive Negative Pulse/Bipolar Violation Output Port 7

SYMBOL

LQFP

FBGA

TYPE

DESCRIPTION

SYMBOL

LQFP

FBGA

TYPE

DESCRIPTION

TTIP0

TRING0

45

46

N5

P5

O

O

Transmit Tip Output Port 0

Transmit Ring Output Port 0

These pins are the differential outputs of the transmit driver.

The driver internally matches impedances for E1 75

Ω

or

E1 120

Ω

lines requiring only a 1:1.15 transformer. The

CBLSEL pin is used to select the appropriate line matching

impedance only in “Hardware” mode. In host mode, the ap-

propriate line matching impedance is selected by the

NOTE: TTIP and TRING are forced to a high impedance state

when the TCLK or the TXOE pin is forced “Low”.

RTIP0

RRING0

48

49

P7

N7

I

I

Receive Tip Input Port 0

Receive Ring Input Port 0

These pins are the differential line inputs to the receiver.

The receiver uses either Internal Line Impedance or Exter-

nal Line Impedance modes to match the line impedances

for E1 75

Ω

or

E1 120

Ω

modes.

Internal Line Impedance Mode - The receiver uses the

same external resistors to match the line impedance (Refer

to

External Line Impedance Mode - The receiver uses differ-

ent external resistors to match the line impedance (Refer to

).

- In host mode, the appropriate line impedance is selected

by the

Line Length Data Register (11h)

14.18 on page 38).

- In hardware mode, the CBLSEL pin selects the appropri-

ate line impedance. (Refer to

for proper

line impedance settings).

NOTE: Data and clock recovered from the signal input on

these pins are output via RCLK, RPOS, and RNEG.

TTIP1

52

L5

O

Transmit Tip Output Port 1

TRING1

51

M5

O

Transmit Ring Output Port 1

RTIP1

55

M7

I

Receive Tip Input Port 1

RRING1

54

L7

I

Receive Ring Input Port 1

TTIP2

57

L10

O

Transmit Tip Output Port 2