Cirrus Logic CS61880 User Manual

Page 13

CS61880

DS450PP3

13

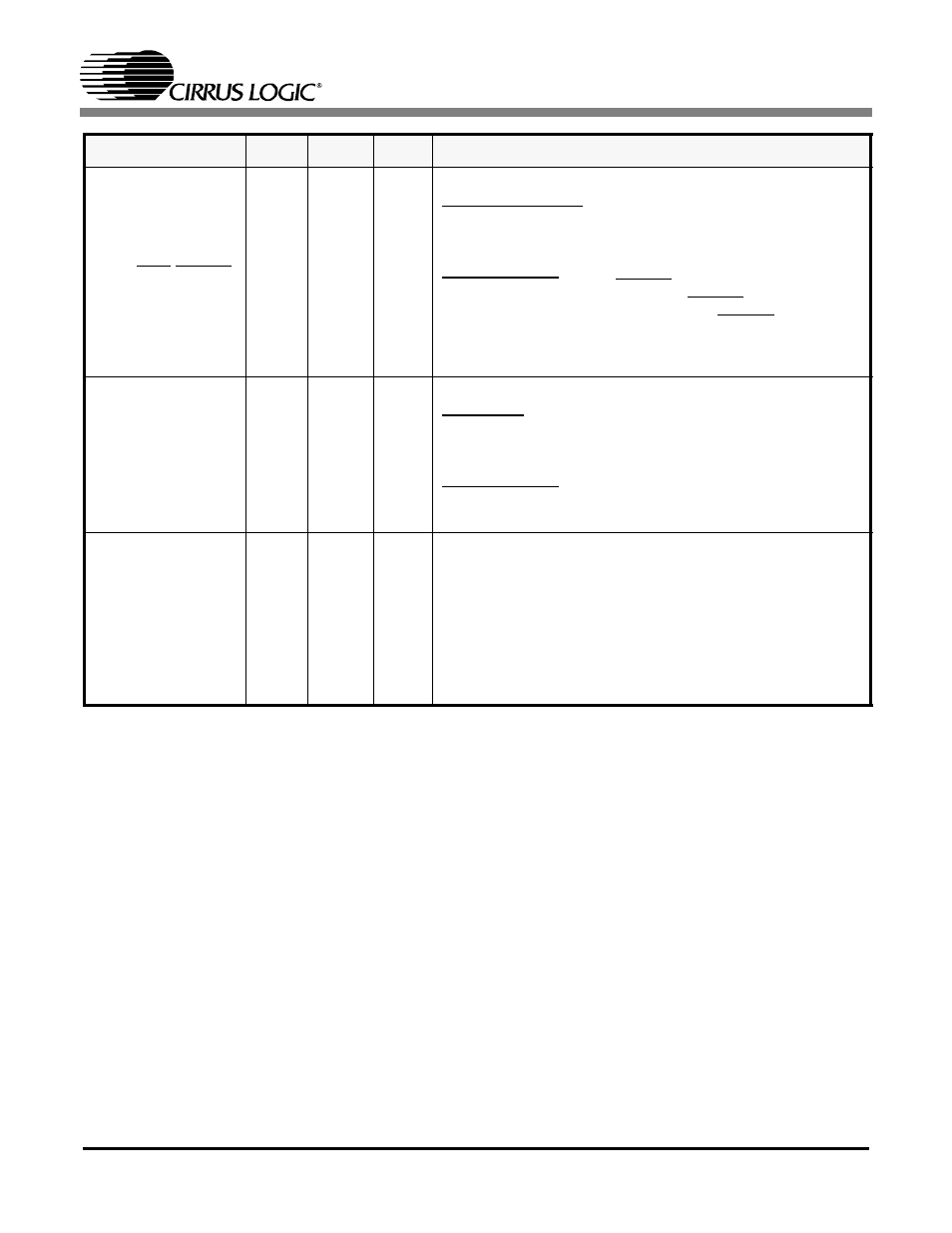

INTL/MOT/CODEN

88

H12

I

Intel/Motorola/Coder Mode Select Input

Parallel Host Mode - When this pin is “Low” the micropro-

cessor interface is configured for operation with Motorola

processors. When this pin is “High” the microprocessor in-

terface is configured for operation with Intel processors.

Hardware Mode - When the CS61880 is configured for uni-

polar operation, this pin, CODEN, configures the line

encoding/decoding function. When CODEN is low, HDB3

encoders/decoders are enabled. When CODEN is high,

AMI encoding/decoding is activated. This is done for all

eight channels.

TXOE

114

E14

I

Transmitter Output Enable

Host mode - Operates the same as in hardware mode. In-

dividual drivers can be set to a high impedance state via

the

page 38).

Hardware Mode - When TXOE pin is asserted Low, all the

TX drivers are forced into a high impedance state. All other

internal circuitry remains active.

CLKE

115

E13

I

Clock Edge Select

In clock/data recovery mode, setting CLKE “high” will cause

RPOS/RNEG to be valid on the falling edge of RCLK and

SDO to be valid on the rising edge of SCLK. When CLKE is

set “low”, RPOS/RNEG is valid on the rising edge of RCLK,

and SDO is valid on the falling edge of SCLK. When the

part is operated in data recovery mode, the RPOS/RNEG

output polarity is active “high” when CLKE is set “high” and

active “low” when CLKE is set “low”.

SYMBOL

LQFP

FBGA

TYPE

DESCRIPTION