Cdb53l30, 6 schematics, Figure 6-2. inputs – Cirrus Logic CDB53L30 User Manual

Page 23: Dc blocking capacitors, Input 2 (analog), Input 1 (analog/digital), Input 4 (analog), Input 3 (analog/digital)

23

DS963DB1

CDB53L30

6 Schematics

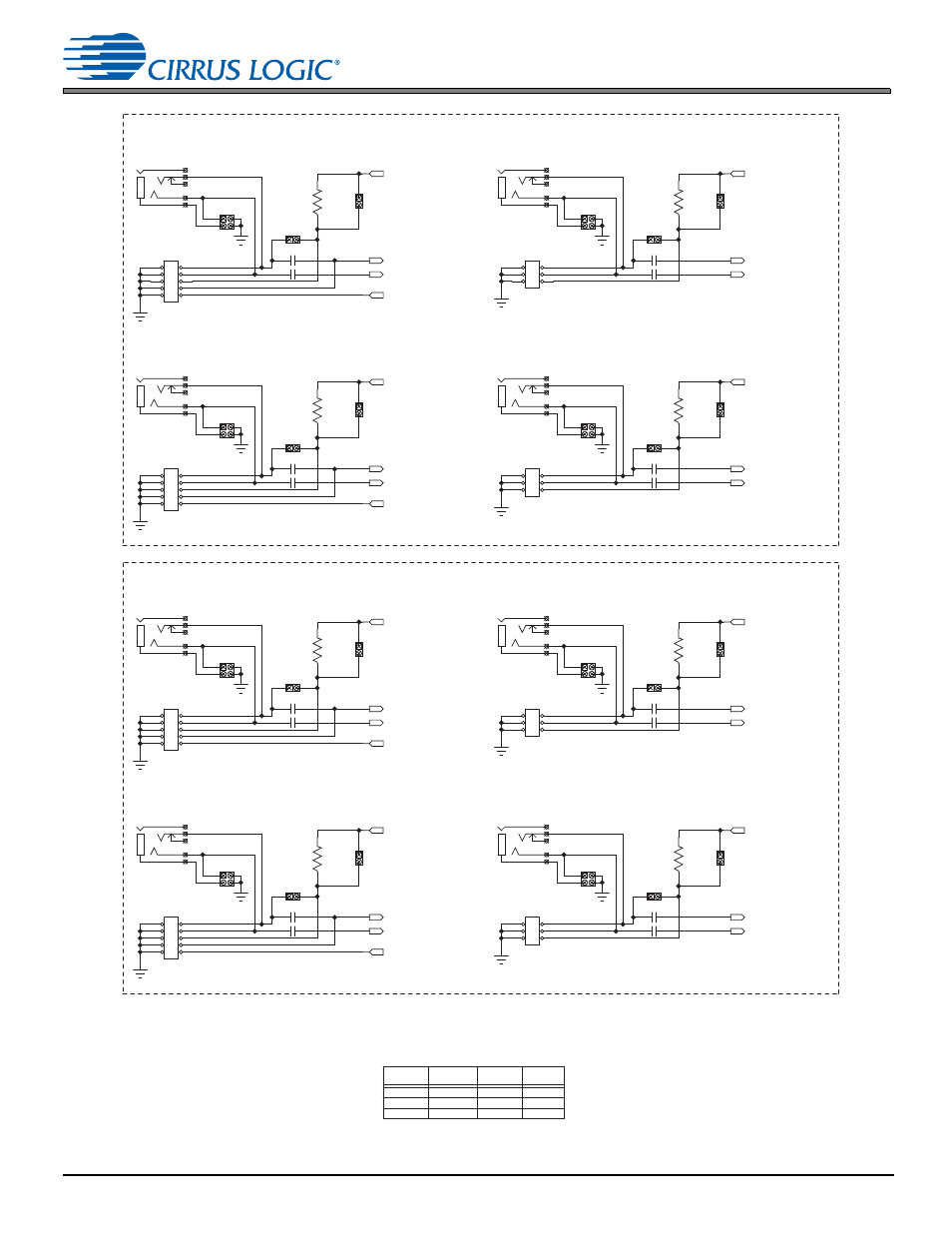

Figure 6-2. Inputs

CS53L30-1

DC Blocking Capacitors

CS53L30 Input

Impedance

Preamp

Setting

DC Blocking

Capacitor

High-Pass

Corner Freq

Bypass

50k

0.1 uF

31.8 Hz

+10 or +20

1M

0.1 uF

1.6 Hz

+10 or +20

1M

0.01 uF

15.9 Hz

The value of the DC blocking capacitor can be modified according

to the desired high-pass corner frequency, determined by the

CS53L30 input impedance. Several example calculations are shown

in the table below.

Sleeve

AIN-

1.AIN2+

1.AIN2-

1.BIAS2

Input 2 (Analog)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

Sleeve

AIN-

1.AIN1+

1.AIN1-

1.BIAS1

1.DATA1

1.SCLK1

Input 1 (Analog/Digital)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

Sleeve

AIN-

1.AIN4+

1.AIN4-

1.BIAS4

Input 4 (Analog)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

Sleeve

AIN-

1.AIN3+

1.AIN3-

1.BIAS3

1.DATA2

1.SCLK2

Input 3 (Analog/Digital)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

CS53L30-2

Sleeve

AIN-

1.AIN2+

1.AIN2-

1.BIAS2

Input 2 (Analog)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

Sleeve

AIN-

1.AIN1+

1.AIN1-

1.BIAS1

1.DATA1

1.SCLK1

Input 1 (Analog/Digital)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

Sleeve

AIN-

1.AIN4+

1.AIN4-

1.BIAS4

Input 4 (Analog)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

Sleeve

AIN-

1.AIN3+

1.AIN3-

1.BIAS3

1.DATA2

1.SCLK2

Input 3 (Analog/Digital)

Bias to AIN+

(Jumper)

Rbias Short

(Jumper)

Rbias

1

2

3

4

5

6

J17

HDR3X2

T

R

6

2

3

4

5

J12

CK-3.5-027A

1.AIN2

C21

0.1uF

X5R

C22

0.1uF

X5R

J3

J43

J44

R51

1.8K

T

R

6

2

3

4

5

J53

CK-3.5-027A

1.AIN1

1

2

3

4

5

6

7

8

9

10

J6

HDR5X2

C20

0.1uF

X5R

C78

0.1uF

X5R

J36

J38

J39

R27

1.8K

1

2

3

4

5

6

J22

HDR3X2

T

R

6

2

3

4

5

J20

CK-3.5-027A

1.AIN4

C25

0.1uF

X5R

C26

0.1uF

X5R

J18

J85

J86

R68

1.8K

T

R

6

2

3

4

5

J16

CK-3.5-027A

1.AIN3

1

2

3

4

5

6

7

8

9

10

J19

HDR5X2

C23

0.1uF

X5R

C24

0.1uF

X5R

J15

J42

J45

R56

1.8K

1

2

3

4

5

6

J25

HDR3X2

T

R

6

2

3

4

5

J23

CK-3.5-027A

2.AIN2

C71

0.1uF

X5R

C72

0.1uF

X5R

J21

J77

J78

R124

1.8K

T

R

6

2

3

4

5

J7

CK-3.5-027A

2.AIN1

1

2

3

4

5

6

7

8

9

10

J11

HDR5X2

C27

0.1uF

X5R

C66

0.1uF

X5R

J10

J72

J73

R69

1.8K

1

2

3

4

5

6

J32

HDR3X2

T

R

6

2

3

4

5

J30

CK-3.5-027A

2.AIN4

C75

0.1uF

X5R

C76

0.1uF

X5R

J27

J41

J46

R169

1.8K

T

R

6

2

3

4

5

J26

CK-3.5-027A

2.AIN3

1

2

3

4

5

6

7

8

9

10

J28

HDR5X2

C73

0.1uF

X5R

C74

0.1uF

X5R

J24

J50

J51

R168

1.8K

CS53L30-1.IN2-

[2]

CS53L30-1.IN2+

[2]

CS53L30-1.MIC2_BIAS

[2]

CS53L30-1.IN1-

[2]

CS53L30-1.IN1+

[2]

CS53L30-1.DMIC1_SCLK [2]

CS53L30-1.MIC1_BIAS

[2]

CS53L30-1.IN4-

[2]

CS53L30-1.IN4+

[2]

CS53L30-1.MIC4_BIAS

[2]

CS53L30-1.IN3-

[2]

CS53L30-1.IN3+

[2]

CS53L30-1.DMIC2_SCLK/AD1 [2]

CS53L30-1.MIC3_BIAS

[2]

CS53L30-2.IN2-

[2]

CS53L30-2.IN2+

[2]

CS53L30-2.MIC2_BIAS

[2]

CS53L30-2.IN1-

[2]

CS53L30-2.IN1+

[2]

CS53L30-2.DMIC1_SCLK [2]

CS53L30-2.MIC1_BIAS

[2]

CS53L30-2.IN4-

[2]

CS53L30-2.IN4+

[2]

CS53L30-2.MIC4_BIAS

[2]

CS53L30-2.IN3-

[2]

CS53L30-2.IN3+

[2]

CS53L30-2.DMIC2_SCLK/AD1 [2]

CS53L30-2.MIC3_BIAS

[2]