6 schematics, Cdb53l30 – Cirrus Logic CDB53L30 User Manual

Page 22

22

DS963DB1

CDB53L30

6 Schematics

6 Schematics

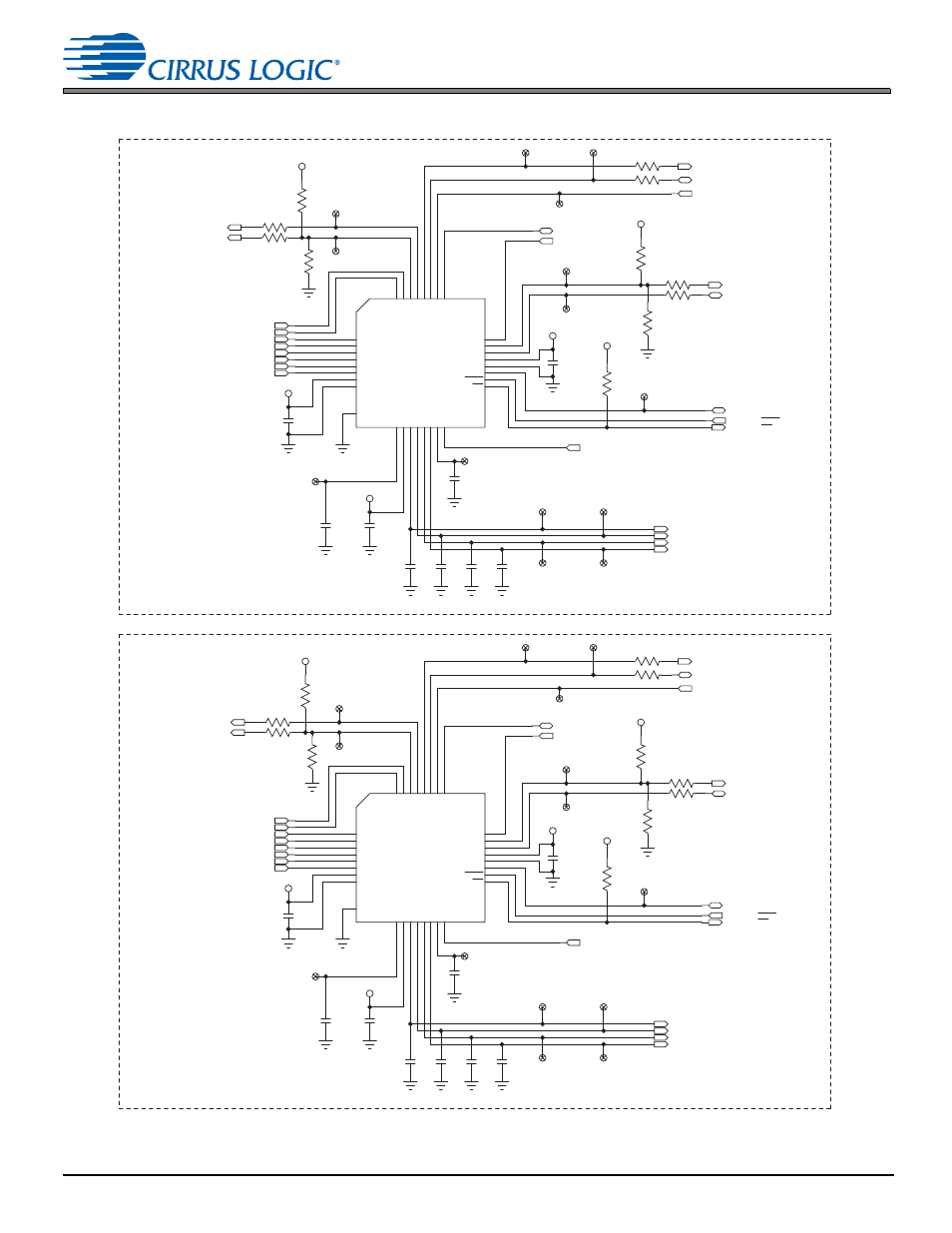

Figure 6-1. CS53L30

I2C Address: 0x90

CS53L30-1

I2C Address: 0x92

CS53L30-2

1

IN2+

2

IN2-

3

IN3+

4

IN3-

5

IN4+

6

IN4-

7

VA

8

GNDA

9

FI

L

T

+

10

VP

11

M

IC

1_B

IA

S

12

M

IC

2_B

IA

S

13

M

IC

3_B

IA

S

14

M

IC

4_B

IA

S

15

MI

C

_

B

IA

S

_

F

IL

T

16

MU

T

E

17

INT

18

RESET

19

SYNC

20

GNDD

21

VA

22

LRCK/FSYNC

23

ASP2_SDOUT/AD0

24

SCL

25

SD

A

26

MC

L

K

27

SC

L

K

28

A

S

P

1_S

D

O

U

T

29

D

M

IC

1_S

C

L

K

30

D

M

IC

2_S

C

L

K/

A

D

1

31

IN

1

+

32

IN

1

-

PAD

THERM

U5

CS53L30-QFN32

C28

2.2uF

X5R

C29

4.7UF

X5R

C31

0.1uF

X5R

C30

0.1uF

X5R

C36

0.1uF

X5R

R21

NO POP

R19

10K

R22

NO POP

R23

10K

TP5

1.MIC_BIAS_FILT

TP6

1.FILT+

R30

10K

TP7

1.MIC1_BIAS

TP9

1.MIC2_BIAS

TP10

1.MIC3_BIAS

TP11

1.MIC4_BIAS

TP12

1.ASP1_SDOUT

TP13

1.SCLK

R59

0

R62

0

R9

0

R29

0

R34

0

R36

0

TP15

1.ASP2_SDOUT/AD0

TP16

1.LRCK/FSYNC

TP17

1.DMIC1_SCLK

TP19

1.DMIC2_SCLK/AD1

TP20

1.SYNC

1

IN2+

2

IN2-

3

IN3+

4

IN3-

5

IN4+

6

IN4-

7

VA

8

GNDA

9

FI

L

T

+

10

VP

11

M

IC

1_B

IA

S

12

M

IC

2_B

IA

S

13

M

IC

3_B

IA

S

14

M

IC

4_B

IA

S

15

MI

C

_

B

IA

S

_

F

IL

T

16

MU

T

E

17

INT

18

RESET

19

SYNC

20

GNDD

21

VA

22

LRCK/FSYNC

23

ASP2_SDOUT/AD0

24

SCL

25

SD

A

26

MC

L

K

27

SC

L

K

28

A

S

P

1_S

D

O

U

T

29

DM

IC

1

_

S

C

L

K

30

D

M

IC

2_S

C

L

K/

A

D

1

31

IN

1

+

32

IN

1

-

PAD

THERM

U22

CS53L30-QFN32

C57

2.2uF

X5R

C58

4.7UF

X5R

C59

0.1uF

X5R

C60

0.1uF

X5R

C61

0.1uF

X5R

R35

NO POP

R37

10K

TP29

2.MIC_BIAS_FILT

TP30

2.FILT+

R95

10K

TP31

2.MIC1_BIAS

TP32

2.MIC2_BIAS

TP33

2.MIC3_BIAS

TP34

2.MIC4_BIAS

TP35

2.ASP1_SDOUT

TP36

2.SCLK

R96

0

R98

0

R101

0

R102

0

R103

0

R105

0

TP37

2.ASP2_SDOUT/AD0

TP38

2.LRCK/FSYNC

TP39

2.DMIC1_SCLK

TP40

2.DMIC2_SCLK/AD1

TP41

2.SYNC

R106

NO POP

R107

10K

C37

1uF

X5R

C38

1uF

X5R

C39

1uF

X5R

C40

1uF

X5R

C62

1uF

X5R

C63

1uF

X5R

C64

1uF

X5R

C65

1uF

X5R

TP14

2.MCLK

TP42

1.MCLK

CS53L30-1.IN2+

[2]

CS53L30-1.IN2-

[2]

CS53L30-1.IN3+

[2]

CS53L30-1.IN3-

[2]

CS53L30-1.IN4+

[2]

CS53L30-1.IN4-

[2]

VA

CS53L30-1.MUTE [5]

CS53L30-1.INT

[5]

CS53L30-1.RESET

[5]

VA

CS53L30.I2C.SDA [2,5]

CS53L30.I2C.SCL [2,5]

CS53L30-1.SCLK

[4]

VA

CS53L30-1.ASP1_SDOUT [4]

CS53L30-1.DMIC1_SCLK

[2]

CS53L30-1.DMIC2_SCLK/AD1

[2]

CS53L30-1.ASP2_SDOUT/AD0 [4]

VA

CS53L30-1.MCLK

[3]

VP

CS53L30-1.MIC1_BIAS

[2]

CS53L30-1.MIC2_BIAS

[2]

CS53L30-1.MIC3_BIAS

[2]

CS53L30-1.MIC4_BIAS

[2]

CS53L30-1.IN1-

[2]

CS53L30-1.IN1+

[2]

VA

CS53L30-1.LRCK/FSYNC

[4]

CS53L30-1.SYNC [3]

CS53L30-2.IN2+

[2]

CS53L30-2.IN2-

[2]

CS53L30-2.IN3+

[2]

CS53L30-2.IN3-

[2]

CS53L30-2.IN4+

[2]

CS53L30-2.IN4-

[2]

VA

CS53L30-2.MUTE [5]

CS53L30-2.INT

[5]

CS53L30-2.RESET

[5]

VA

CS53L30.I2C.SDA

[2,5]

CS53L30.I2C.SCL

[2,5]

CS53L30-2.SCLK

[4]

VA

CS53L30-2.ASP1_SDOUT [4]

CS53L30-2.DMIC1_SCLK

[2]

CS53L30-2.DMIC2_SCLK/AD1

[2]

CS53L30-2.ASP2_SDOUT/AD0 [4]

VA

CS53L30-2.MCLK

[3]

VP

CS53L30-2.MIC1_BIAS

[2]

CS53L30-2.MIC2_BIAS

[2]

CS53L30-2.MIC3_BIAS

[2]

CS53L30-2.MIC4_BIAS

[2]

CS53L30-2.IN1-

[2]

CS53L30-2.IN1+

[2]

VA

CS53L30-2.LRCK/FSYNC

[4]

CS53L30-2.SYNC

[3]