5 performance plots, Cdb53l30 – Cirrus Logic CDB53L30 User Manual

Page 17

17

DS963DB1

CDB53L30

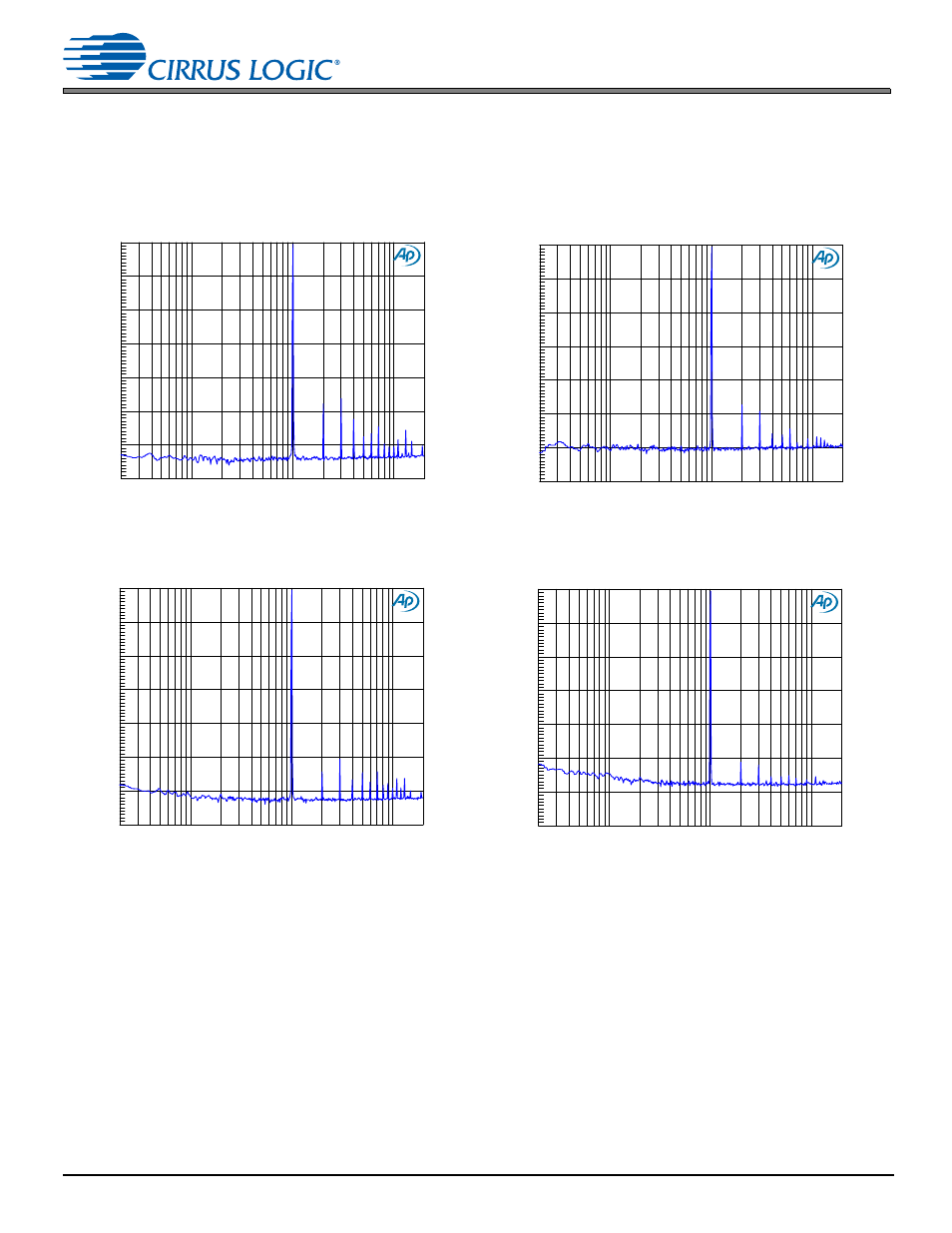

5 Performance Plots

5 Performance Plots

Test conditions (unless otherwise specified): FS

ext

= 48 kHz; MCLK

ext

= 12.2880 MHz; preamp setting: 0 dB (bypassed);

PGA setting: 0 dB; high-pass filter enabled, ADCx_HPF_CF = 00; notch filter disabled; noise gate disabled; MCLK

autoscale enabled; VA = 1.8 V, VP = 3.6 V. THD+N measurement bandwidth = 10 Hz to FS

ext

/2, no weighting. Unless

otherwise specified, the performance data is representative of all channels on both CS53L30 devices.

Figure 5-1. Output FFT, Preamp Setting: 0 dB,

PGA Setting: 0 dB, 1 kHz, –1 dBFS

Figure 5-2. Output FFT, Preamp Setting: 0 dB,

PGA Setting: +12 dB, 1 kHz, –1 dBFS

Figure 5-3. Output FFT, Preamp Setting: +10 dB,

PGA Setting: 0 dB, 1 kHz, –1 dBFS

Figure 5-4. Output FFT, Preamp Setting: +10 dB,

PGA Setting: +12 dB, 1 kHz, –1 dBFS

G

%

)

6

N

N

N

N

N

+]

G

%

)

6

N

N

N

N

N

+]

G

%

)

6

N

N

N

N

N

+]

G

%

)

6

N

N

N

N

N

+]

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)