Iir filter, 1 iir architecture, 2 iir1 filter – Cirrus Logic CS5378 User Manual

Page 52: 3 iir2 filter, Iir architecture, Iir1 filter, Iir2 filter, Figure 30. iir filter block diagram, Cs5378

CS5378

DS639F3

52

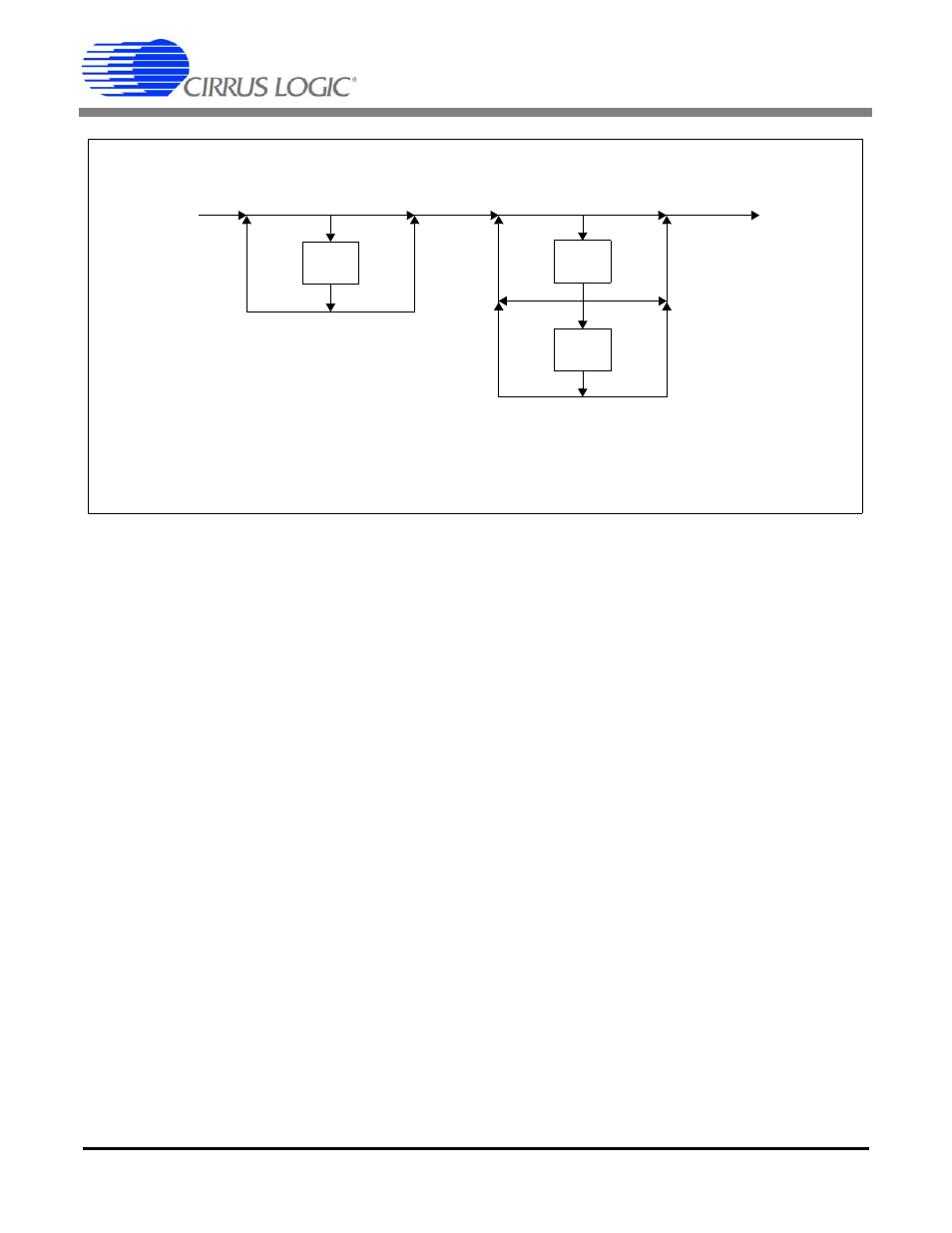

14. IIR FILTER

The infinite impulse response (IIR) filter block

consists of two cascaded stages, IIR1 and IIR2. It

creates a high-pass corner to block very low-fre-

quency and DC components of the input signal.

On-chip IIR1 and IIR2 coefficients can be selected

using a configuration command, or the coefficients

can be programmed for a custom filter response.

14.1 IIR Architecture

The architecture of the IIR filter is automatically

determined when the output filter stage is selected

in the FILTCFG register. Selecting the 1st order

IIR1 filter bypasses the 2nd order stage, while se-

lecting the 2nd order IIR2 filter bypasses the 1st or-

der stage. Selection of the 3rd order IIR3 filter

enables both the 1st and 2nd order stages.

14.2 IIR1 Filter

The 1st order IIR filter stage is a direct form filter

with three coefficients: a11, b10, and b11. Coeffi-

cients of a 1st order IIR are inherently normalized

to one, and should be scaled to 24-bit two’s com-

plement full scale, 0x7FFFFF.

The characteristic equations for the 1st order IIR

include an input value, X, an output value, Y, and

two intermediate values, W1 and W2, separated by

a delay element (z

-1

).

W2 = W1

W1 = X + (-a11 * W2)

Y = (W1 * b10) + (W2 * b11)

14.3 IIR2 Filter

The 2nd order IIR filter stage is a direct form filter

with five coefficients: a21, a22, b20, b21, and b22.

Coefficients of a 2nd order IIR are inherently nor-

malized to two, and should be scaled to 24-bit

two’s complement full scale, 0x7FFFFF. Normal-

ization effectively divides the 2nd order coeffi-

cients in half relative to the input, and requires

modification of the characteristic equations.

The characteristic equations for the 2nd order IIR

include an input value, X, an output value, Y, and

three intermediate values, W3, W4, and W5, each

separated by a delay element (z

-1

). The following

Z

-1

Z

-1

Z

-1

-a

11

b

11

b

10

-a

21

-a

22

b

21

b

22

b

20

Figure 30. IIR Filter Block Diagram

1st Order IIR1

2nd Order IIR2

3rd Order IIR3 implemented by

running both IIR1 and IIR2 stages