Digital filter initialization, 1 filter coefficient selection, 2 filter configuration options – Cirrus Logic CS5378 User Manual

Page 38: Filter coefficient selection, Filter configuration options, Figure 21. digital filter stages, Cs5378

CS5378

DS639F3

38

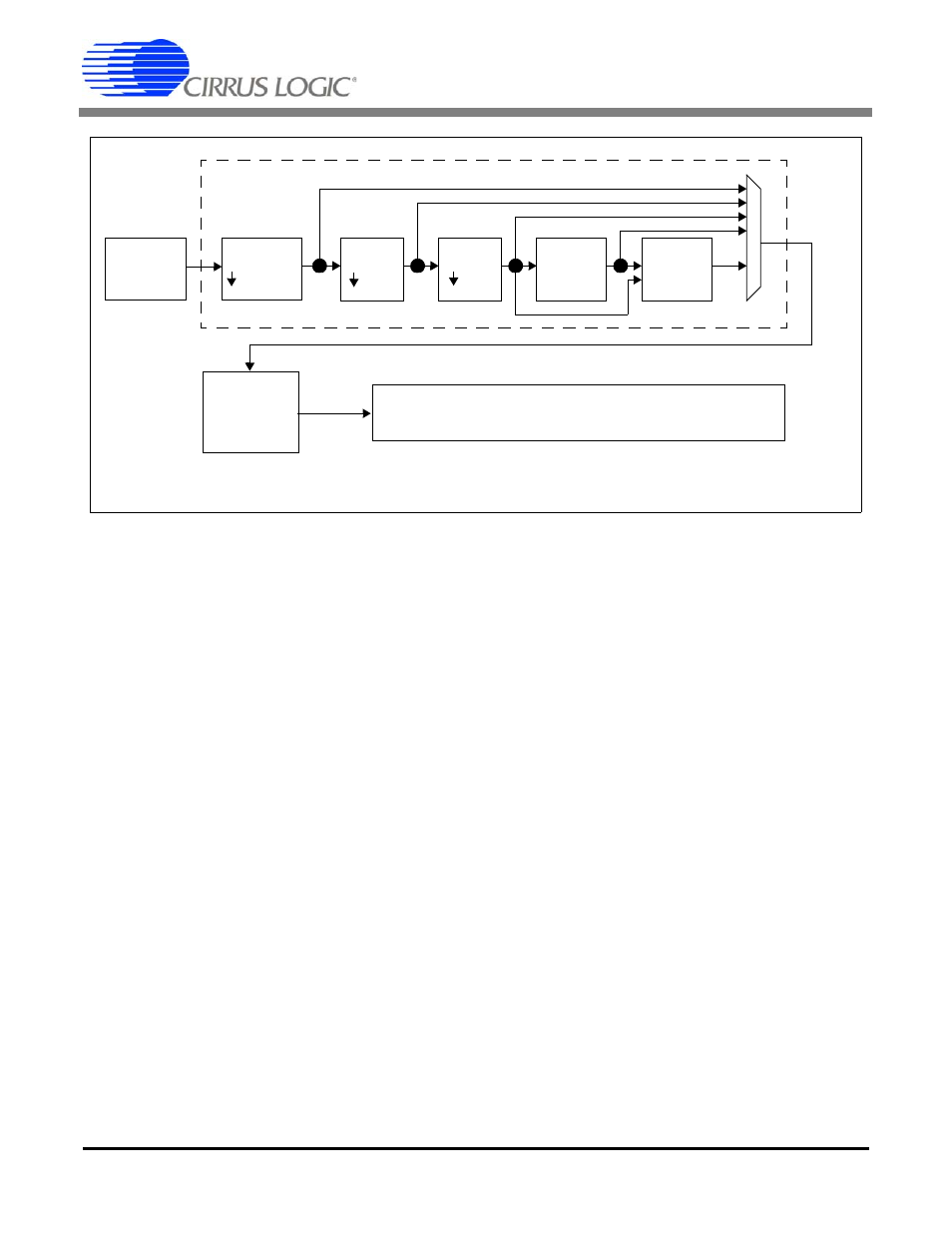

11. DIGITAL FILTER INITIALIZATION

The CS5378 digital filter consists of three multi-

stage sections: a three stage SINC filter, a two stage

FIR filter, and a two stage IIR filter.

To initialize the digital filter, FIR and IIR coeffi-

cient sets are selected using configuration com-

mands and the FILTCFG register (0x20) is written

to select the output filter stage, the output word

rate, and the number of enabled channels. The dig-

ital filter clock rate is then selected by writing the

CONFIG register (0x00).

11.1 Filter Coefficient Selection

Selection of SINC filter coefficients is not required

as they are selected automatically based on the pro-

grammed output word rate.

Digital filter FIR and IIR coefficients are selected

using the ‘Write FIR Coefficients’ and ‘Write IIR

Coefficients’, or the ‘Write ROM Coefficients’

configuration commands. When writing the FIR

and IIR coefficients from ROM, a data word selects

an on-chip coefficient set for each filter stage. Fig-

ure 22 shows the format of the coefficient selection

word, and the available coefficient sets for each se-

lection.

Characteristics of the on-chip digital filter coeffi-

cients are discussed in the ‘SINC Filter’, ‘FIR Fil-

ter’, and ‘IIR Filter’ sections of this data sheet.

11.2 Filter Configuration Options

Digital filter parameters are selected by bits in the

FILTCFG register (0x20), and the digital filter

clock rate is selected by bits in the CONFIG regis-

ter (0x00).

11.2.1 Output Filter Stage

The digital filter can output data following any

stage in the filter chain. The output filter stage is

selected by the FSEL bits in the FILTCFG register.

Taking data from the SINC or FIR1 filter stages re-

duces the overall decimation of the filter chain and

increases the output rate, as discussed in the next

section. Taking data from FIR2, IIR1, IIR2, or IIR3

results in data at the selected rate.

Figure 21. Digital Filter Stages

SINC Filter

2 - 64000

FIR1

4

FIR2

2

IIR1

IIR2

1st Order

2nd Order

Output to High Speed Serial Data Interface

DC Offset

Correction

Output Rate 4000 SPS ~ 1 SPS

& Gain

Modulator

512 kHz

Input