Modulator interface, 1 pin descriptions, 2 modulator clock generation – Cirrus Logic CS5378 User Manual

Page 36: 3 modulator synchronization, Pin descriptions, Modulator clock generation, Modulator synchronization, Figure 20. modulator data interface, Cs5378

CS5378

DS639F3

36

10. MODULATOR INTERFACE

The CS5378 performs digital filtering for a

ΔΣ type

modulator. Signals from the

ΔΣ modulators are

connected through the modulator data interface

(MDI).

10.1 Pin Descriptions

MCLK - Pin 11

Modulator clock output. Nominally 2.048 MHz or

1.024 MHz.

MSYNC - Pin 12

Modulator synchronization signal output. Generat-

ed from the SYNC input.

MDATA - Pin 13

Modulator data input, nominally 512 kbit/s.

MFLAG - Pin 14

Modulator flag input. Driven high when the mod-

ulator is unstable due to an analog over-range con-

dition.

10.2 Modulator Clock Generation

The MCLK output is a low-jitter, low-skew modu-

lator clock generated from the 32.768 MHz master

clock.

MCLK typically operates at 2.048 MHz unless an-

alog low-power modes require a 1.024 MHz mod-

ulator clock.

The MCLK rate is selected and the MCLK output

is enabled by bits in the digital filter CONFIG reg-

ister (0x00). By default MCLK is disabled and

driven low.

10.3 Modulator Synchronization

The MSYNC output signal follows an input to the

SYNC pin. MSYNC phase aligns the modulator

sampling instant to guarantee synchronous analog

sampling across a measurement network.

MSYNC is enabled by a bit in the CONFIG register

(0x00). By default SYNC inputs do not cause an

MSYNC output.

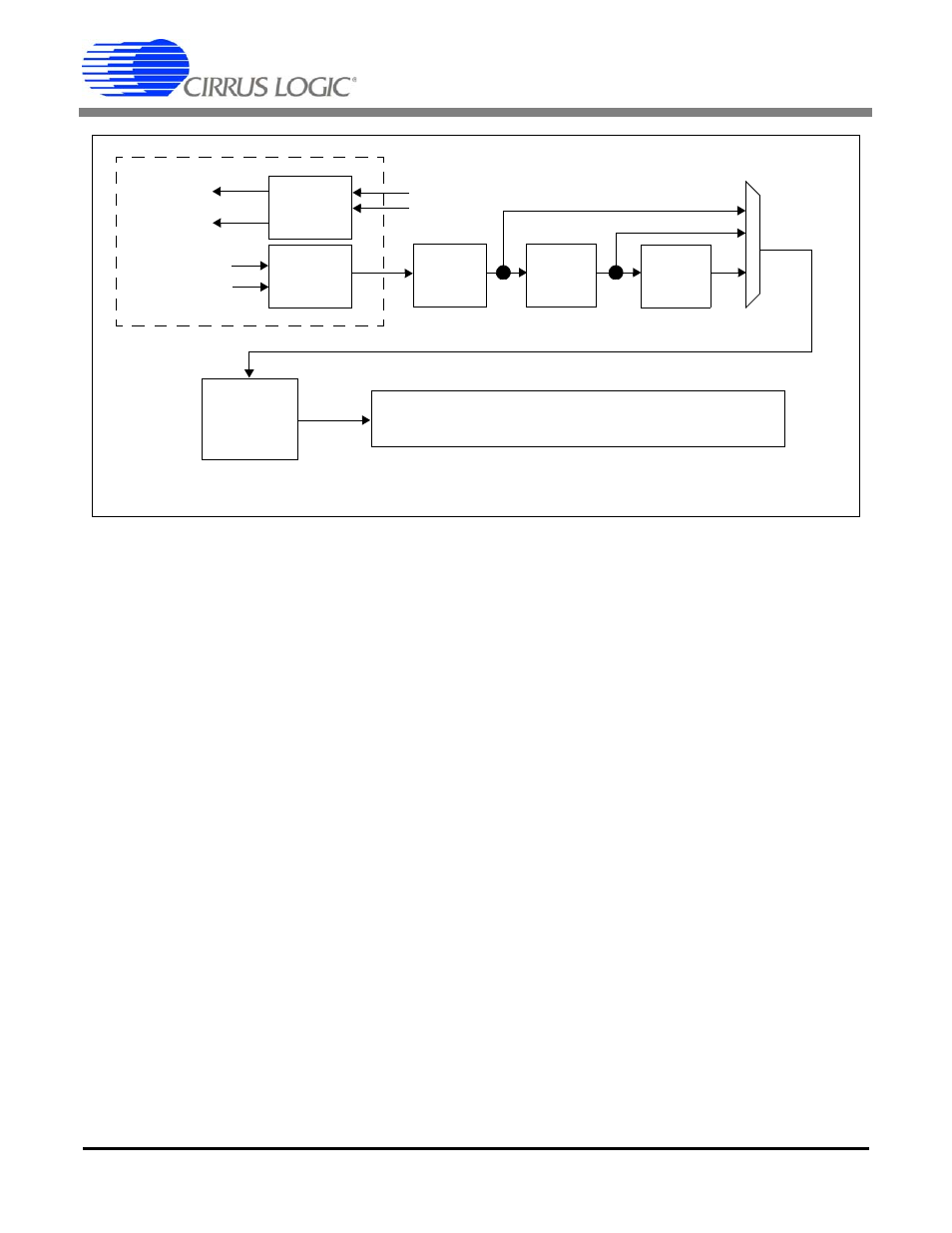

Figure 20. Modulator Data Interface

FIR

IIR

Filters

Filter

Output to High Speed Serial Interface

DC Offset

Correction

Output Rate 4000 SPS ~ 1 SPS

& Gain

MDATA

MFLAG

MDI Input

512 kHz

MCLK /

Generate

MSYNC

CLK

SYNC

MSYNC

SINC

Filter

MCLK