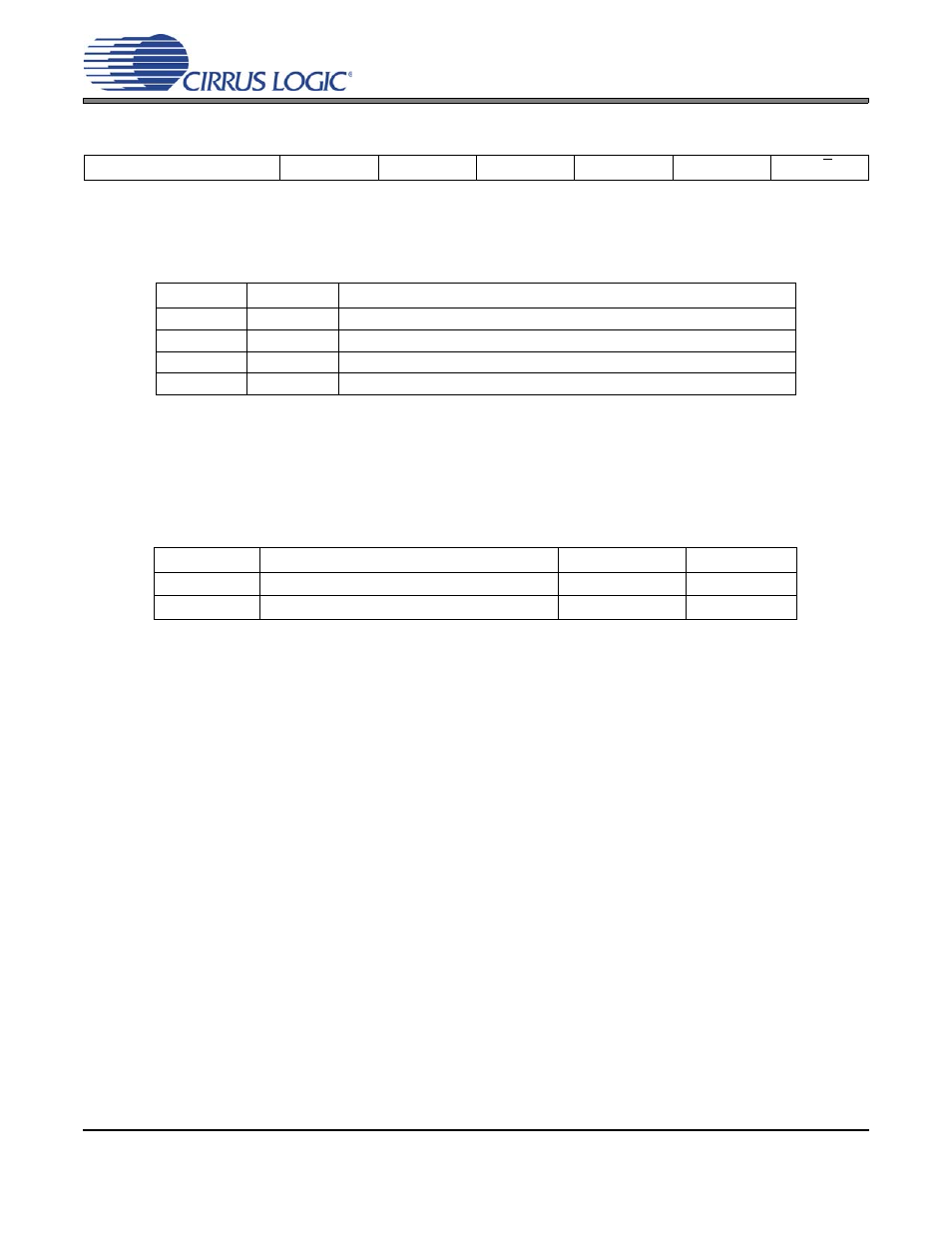

3 adc control - address 04h, 1 functional mode (bits 7:6), Table 6. functional mode selection – Cirrus Logic CS5346 User Manual

Page 29: 2 digital interface format (bit 4), Table 7. digital interface formats, 3 mute (bit 2), 4 high-pass filter freeze (bit 1), 5 master / slave mode (bit 0), Bits (see, Func

DS861PP3

29

CS5346

7.3

ADC Control - Address 04h

7.3.1

Functional Mode (Bits 7:6)

Function:

Selects the required range of sample rates.

7.3.2

Digital Interface Format (Bit 4)

Function:

The required relationship between LRCK, SCLK and SDOUT is defined by the Digital Interface Format

bit. The options are detailed in

and may be seen in

and

.

7.3.3

Mute (Bit 2)

Function:

When this bit is set, the serial audio output of the both channels is muted.

7.3.4

High-Pass Filter Freeze (Bit 1)

Function:

When this bit is set, the internal high-pass filter is disabled. The current DC offset value will be frozen and

continue to be subtracted from the conversion result. See

“High-Pass Filter and DC Offset Calibration” on

7.3.5

Master / Slave Mode (Bit 0)

Function:

This bit selects either master or slave operation for the serial audio port. Setting this bit selects Master

Mode, while clearing this bit selects Slave Mode.

7

6

5

4

3

2

1

0

FM1

FM0

Reserved

DIF

Reserved

Mute

HPFFreeze

M/S

FM1

FM0

Mode

0

0

Single-Speed Mode: 8 to 50 kHz sample rates

0

1

Double-Speed Mode: 50 to 100 kHz sample rates

1

0

Quad-Speed Mode: 100 to 200 kHz sample rates

1

1

Reserved

Table 6. Functional Mode Selection

DIF

Description

Format

Figure

0

Left-Justified (default)

0

1

I²S

1

Table 7. Digital Interface Formats