2 powerdown controls, Table 24. powerdown pr bit functions, Cs4205 – Cirrus Logic CS4205 User Manual

Page 60

CS4205

60

DS489PP4

10.2

Powerdown Controls

The

Powerdown Control/Status Register

(Index 26h) controls the power management func-

tions. The PR[5:0] bits in this register control the

internal powerdown states of the CS4205. Power-

down control is available for individual subsections

of the CS4205 by asserting any PRx bit or any com-

bination of PRx bits. All powerdown states except

PR4 and PR5 can be resumed by clearing the cor-

responding PRx bit. Table 24 shows the mapping

of the power control bits to the functions they man-

age.

When PR0 is ‘set’, the L/R ADCs and the Input

Mux are shut down and the ADC bit in the Power-

down Control/Status Register (Index 26h) is

‘cleared’ indicating the ADCs are no longer in a

ready state. The same is true for PR1 and the

DACs, PR2 and the analog mixer, and PR3 and the

voltage reference (Vrefout). When one of these bits

is ‘cleared’, the corresponding subsystem will be-

gin a power-on process, and the associated status

bit will be ‘set’ when the hardware is ready.

In a primary codec the PR4 bit powers down the

AC-link, but all other analog and digital sub-

systems continue to function. The required resume

sequence from a PR4 state is either a Warm Reset

or a New Warm Reset, depending on whether a

D3

hot

or D3

cold

state has been entered.

The PR5 bit disables all internal clocks and powers

down the DACs and the ADCs, but maintains oper-

ation of the BIT_CLK and the analog mixer. A

Cold Reset is the only way to restore operation to

the CS4205 after asserting PR5. To achieve a com-

plete digital powerdown, PR4 and PR5 must be as-

serted within a single AC output frame. This will

also drive BIT_CLK ‘low’.

The CS4205 does not automatically mute any input

or output when the powerdown bits are ‘set’. The

software driver controlling the AC ’97 device must

manage muting the input and output analog signals

before putting the part into any power management

state. The definition of each PRx bit may affect a

single subsection or a combination of subsections

within the CS4205. Table 25 contains the matrix of

subsections affected by the respective PRx func-

tion. Table 26 shows the different operating power

consumptions levels for different powerdown func-

tions.

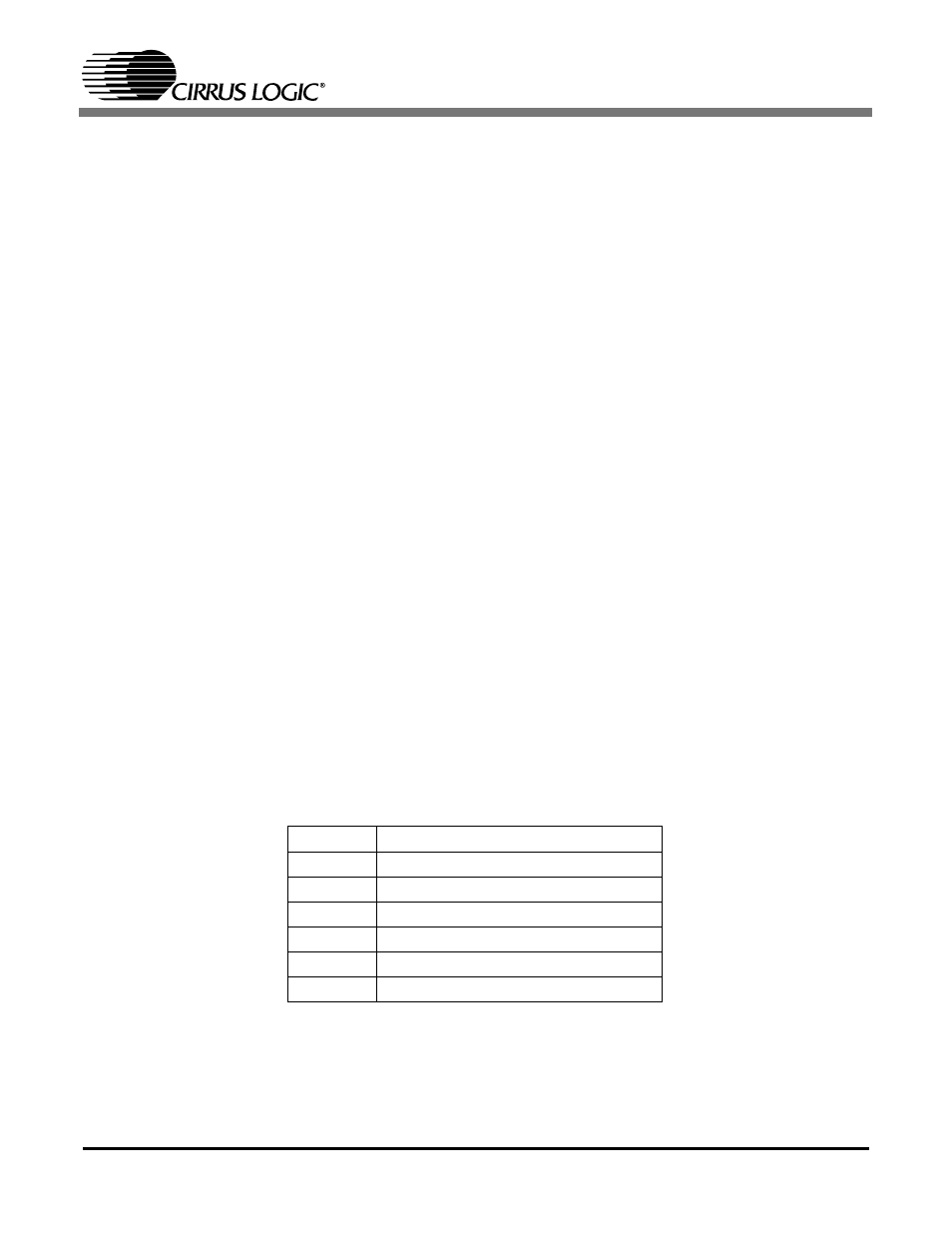

PR Bit

Function

PR0

L/R ADCs and Input Mux Powerdown

PR1

Front DACs Powerdown

PR2

Analog Mixer Powerdown (Vref on)

PR3

Analog Mixer Powerdown (Vref off)

PR4

AC-link Powerdown (BIT_CLK off)*

PR5

Internal Clock Disable

* Applies only to primary codec

Table 24. Powerdown PR Bit Functions