Cs4205 – Cirrus Logic CS4205 User Manual

Page 50

CS4205

50

DS489PP4

5.34

Internal Error Condition Control/Status Registers (Index 6Eh, Address 09h - 0Bh)

EROF

Effects Engine Right Channel Overflow

ELOF

Effects Engine Left Channel Overflow

MROF

Digital Mixer Right Channel Overflow

MLOF

Digital Mixer Left Channel Overflow

AMOR

Mic ADC Overrange

AROR

L/R ADC Right Channel Overrange

ALOR

L/R ADC Left Channel Overrange

Default

0000h

The IEC Config Register (Index 6Eh, Address 09h) enables error signaling for each potential error source. If a bit is

‘clear’, the corresponding source will not be monitored for errors. If a bit is ‘set’, the corresponding source will be

monitored and is able to signal an error condition. If an error occurs, the corresponding bit in the IEC Status Register

(Index 6Eh, Address 0Bh) will be ‘set’ and remains ‘set’ until the error is cleared, even if the error condition is no

longer present. This behavior is equivalent to “sticky” (edge sensitive) GPIO input pins.

The IEC Wakeup Register (Index 6Eh, Address 0Ah)

provides a mask for determining if an IEC will generate a wake-

up or GPIO_INT. If a bit is ‘0’, the corresponding error condition will not generate an interrupt. If a bit is ‘set’, the

corresponding error condition will generate an interrupt. For details about wakeup interrupts refer to the GPIO Pin

Wakeup Mask Register (Index 52h).

The IEC Status Register (Index 6Eh, Address 0Bh)

reflects the state of all internal error conditions. If a bit is ‘clear’,

the corresponding source has not encountered an error condition or is not being monitored for errors. If a bit is ‘set’,

the corresponding source has encountered an error condition. The IEC bit in input slot 12 is a logic OR of all bits in

this register. An error condition is cleared by writing a ‘0’ to the corresponding bit of this register. Before clearing an

error condition, the controller should correct the error to prevent repeated error signaling. Table 20 lists all the inter-

nal error sources and corrective measures for each source.

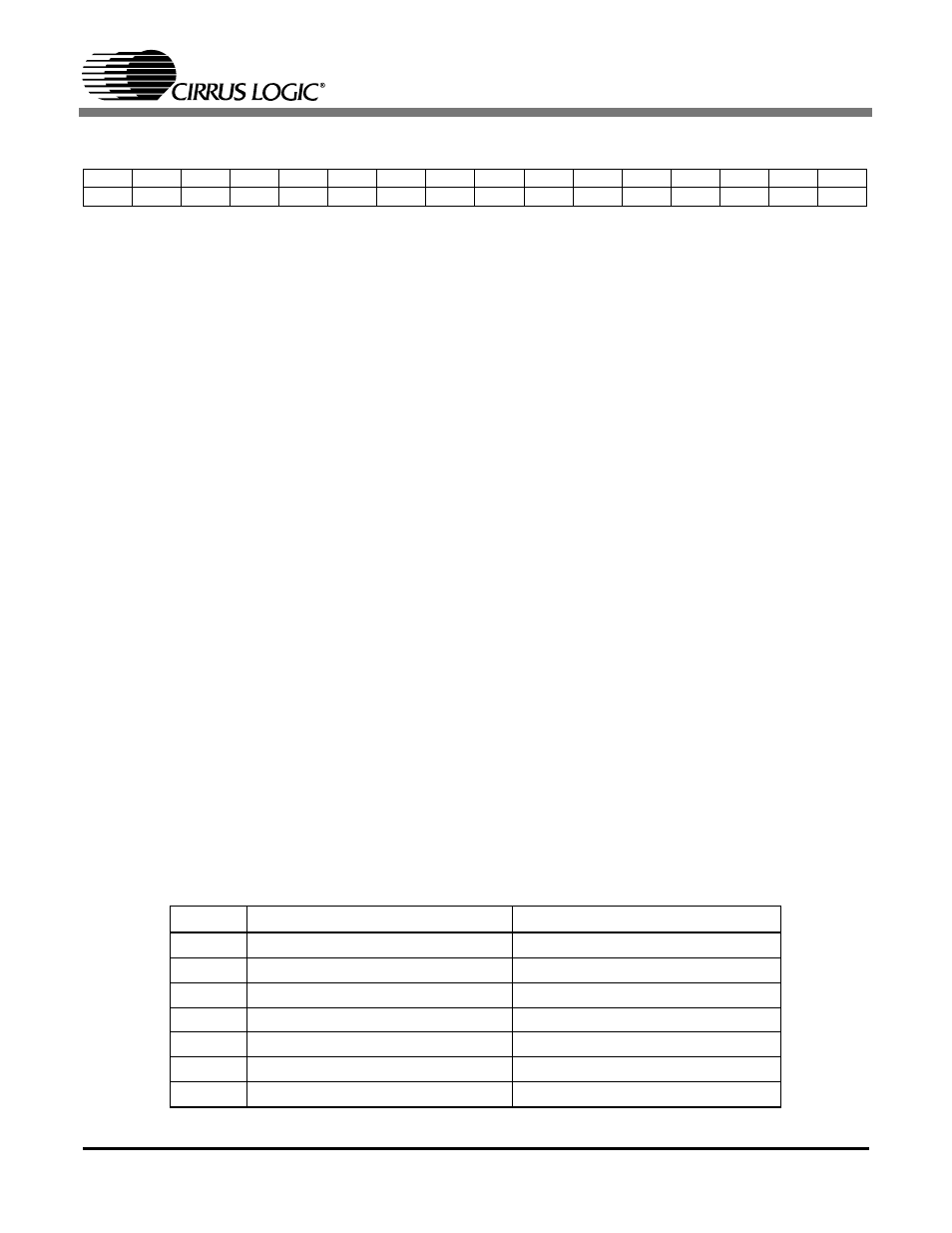

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

EROF ELOF MROF MLOF

0

AMOR AROR ALOR

0

0

0

0

0

0

0

0

IEC Bit

Error Source

Correction Method

ALOR

L/R ADC left channel overrange

GL[3:0] bits in reg 1Ch

AROR

L/R ADC right channel overrange

GR[3:0] bits in reg 1Ch

AMOR

Mic ADC overrange

GM[3:0] bits in reg 1Eh

MLOF

Digital mixer left channel overflow

GL[5:0] bits in reg 6Eh, addr 00h-05h

MROF

Digital mixer right channel overflow

GR[5:0] bits in reg 6Eh, addr 00h-05h

ELOF

Effects engine left channel overflow

GL[3:0] bits in reg 6Eh, addr 08h

EROF

Effects engine right channel overflow GR[3:0] bits in reg 6Eh, addr 08h

Table 20. Internal Error Sources and Correction Methods