27 s/pdif control register (index 68h), Cs4205 – Cirrus Logic CS4205 User Manual

Page 45

CS4205

DS489PP4

45

5.27

S/PDIF Control Register (Index 68h)

SPEN

S/PDIF Enable. The SPEN bit enables S/PDIF data transmission on the SPDO/SDO2 pin.

The SPEN bit routes the left and right channel data from the AC ’97 controller, the digital mix-

er, or the digital effects engine to the S/PDIF transmitter block. The actual data routed to the

S/PDIF block are controlled through the SPDS[1:0]/AMAP/SM[1:0] configuration in the AC

Mode Control Register (Index 5Eh). This bit can only be ‘set’ if the SDO2 bit in the Serial Port

Control Register (Index 6Ah) is ‘0’. If the SDO2 bit is ‘set’, SPEN is a read-only bit and always

returns ‘0’.

Val

Validity. The Val bit is mapped to the V bit (bit 28) of every sub-frame. If this bit is ‘clear’, the

signal is suitable for conversion or processing.

Fs

Sample Rate. The Fs bit indicates the sampling rate for the S/PDIF data. The inverse of this

bit is mapped to bit 25 of the channel status block. When the Fs bit is ‘clear’, the sampling

frequency is 48 kHz. When ‘set’, the sampling frequency is 44.1 kHz. The actual rate at which

S/PDIF data are being transmitted solely depends on the master clock frequency of the

CS4205. The Fs bit is merely an indicator to the S/PDIF receiver.

L

Generation Status. The L bit is mapped to bit 15 of the channel status block. For category

codes 001xxxx, 0111xxx and 100xxxx, a value of ‘0’ indicates original material and a value of

‘1’ indicates a copy of original material. For all other category codes the definition of the L bit

is reversed.

CC[6:0]

Category Code. The CC[6:0] bits are mapped to bits 8-14 of the channel status block.

Emph

Data Emphasis. The Emph bit is mapped to bit 3 of the channel status block. When ‘set’,

50/15 µs filter pre-emphasis is indicated. When is ‘clear’, no pre-emphasis is indicated.

Copy

Copyright. The Copy bit is mapped to bit 2 of the channel status block. If the Copy bit is ‘set’

copyright is not asserted and copying is permitted.

/Audio

Audio / Non-Audio. The /Audio bit is mapped to bit 1 of the channel status block. If the /Audio

bit is ‘clear’, the data transmitted over S/PDIF is assumed to be digital audio. If the /Audio bit

is ‘set’, non-audio data is assumed.

Pro

Professional/Consumer. The Pro bit is mapped to bit 0 of the channel status block. If the Pro

bit is ‘clear’, consumer use of the audio control block is indicated. If the bit is ‘set’, professional

use is indicated.

Default

0000h

For a further discussion of the proper use of the channel status bits see application note AN22: Overview of Digital

Audio Interface Data Structures [3].

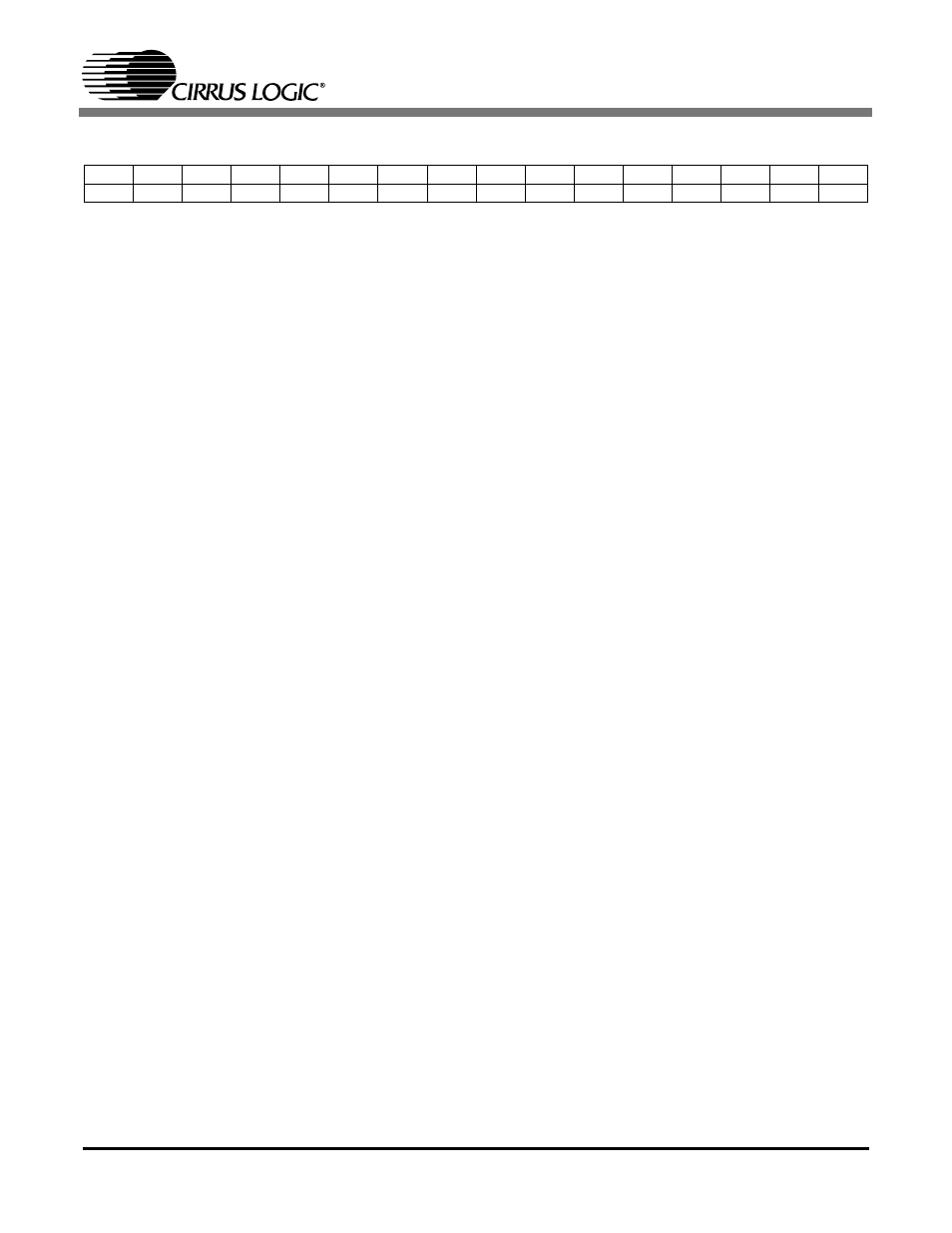

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

SPEN

Val

0

Fs

L

CC6

CC5

CC4

CC3

CC2

CC1

CC0

Emph

Copy /Audio

Pro