Zv port, Figure 21. zv port format (i2s, 16-bit data), E section 7 – Cirrus Logic CS4205 User Manual

Page 57: Cs4205

CS4205

DS489PP4

57

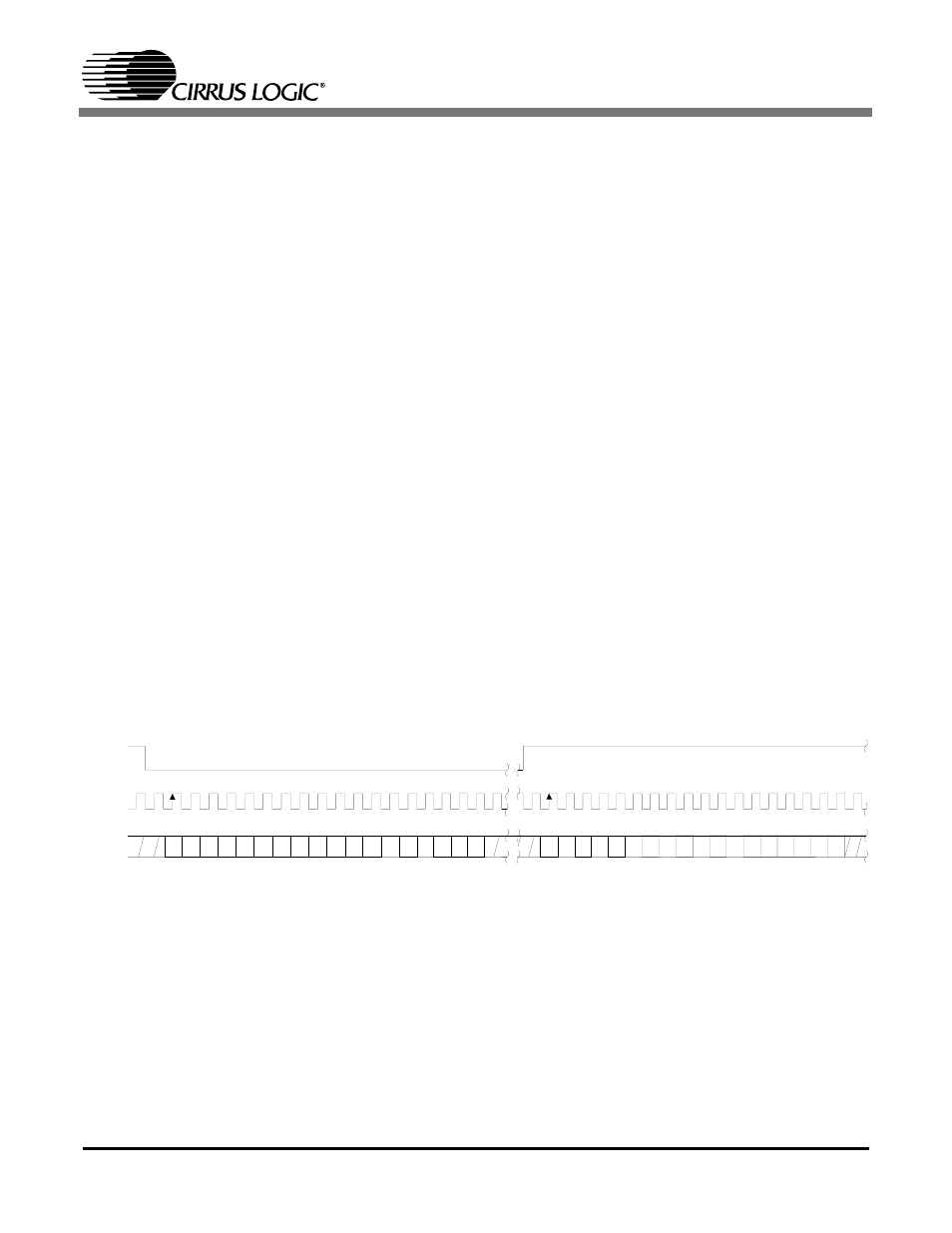

7. ZV PORT

The CS4205 implements an asynchronous serial

data input port that conforms to the Zoomed Video

Port (ZV Port) specification. ZV Port data is asyn-

chronous I

2

S data in PCM format with 16 bits of

resolution. The ZV Port interface consists of four

signals: MCLK, SCLK, LRCLK, and SDATA.

However, the CS4205 does not require a connec-

tion to the asynchronous MCLK. The other three

signals are respectively received on ZSCLK, ZLR-

CLK, and ZSDATA. Although the ZV Port speci-

fication calls for SCLK running at 32 Fs, the

CS4205 supports any SCLK from 32 Fs up to

128 Fs. In all cases, only the first 16 bits of each

channel will be recovered from the incoming serial

data stream. Figure 21 shows the ZV Port format.

The ZV Port is controlled by the ZVEN, LOCK,

and Ph[24:0] bits in the ZV Port Control/Status

Registers (Index 6Eh, Address 0Eh - 0Fh).

Since the data received on the ZV Port is asynchro-

nous and at varying sample rates, it must be sample

rate converted before being sent to the digital mix-

er. The asynchronous SRC is similar in function to

the synchronous DAC SRC, but differs in the way

samples are received and how the sample rate is de-

termined. While the synchronous SRC is being pro-

grammed to the desired sample rate by the host and

requests samples from the host at the programmed

rate, the asynchronous SRC receives data from a

push source at an unknown rate. Therefore, the

asynchronous SRC must determine the rate of in-

coming data and calculate the necessary parame-

ters. The current sample rate can be determined

from the Ph[24:0] bits in the ZV Port Control/Sta-

tus Registers (Index 6Eh, Address 0Eh - 0Fh) by

Fs

in

= Fs

out

*Ph/16,777,216, where Fs

out

is

48 kHz. Once the rate estimator has settled, the

LOCK bit will be asserted. If the incoming clock

rate changes, LOCK will be de-asserted until the

rate estimator has settled again. Settling may take

up to 400 ms. As long as the receiver is unlocked,

the ZV input to the digital mixer will be muted, re-

gardless of the state of the ZV mute bit in the Dig-

ital Mixer Input Volume Register (Index 6E,

Address 00h - 05h).

ZLRCK

ZSCLK

Left Channel

Right Channel

ZSDATA

6

5

4

3

2

1 0

9

8

7

15 14 13 12 11 10

6 5

4 3

2 1

0

9 8 7

15 14 13 12 11 10

Figure 21. ZV Port Format (I

2

S, 16-bit data)