Figure 17. serial data format 0 (i2s), Figure 18. serial data format 1 (left justified), Table 23 sh – Cirrus Logic CS4205 User Manual

Page 56: Cs4205

CS4205

56

DS489PP4

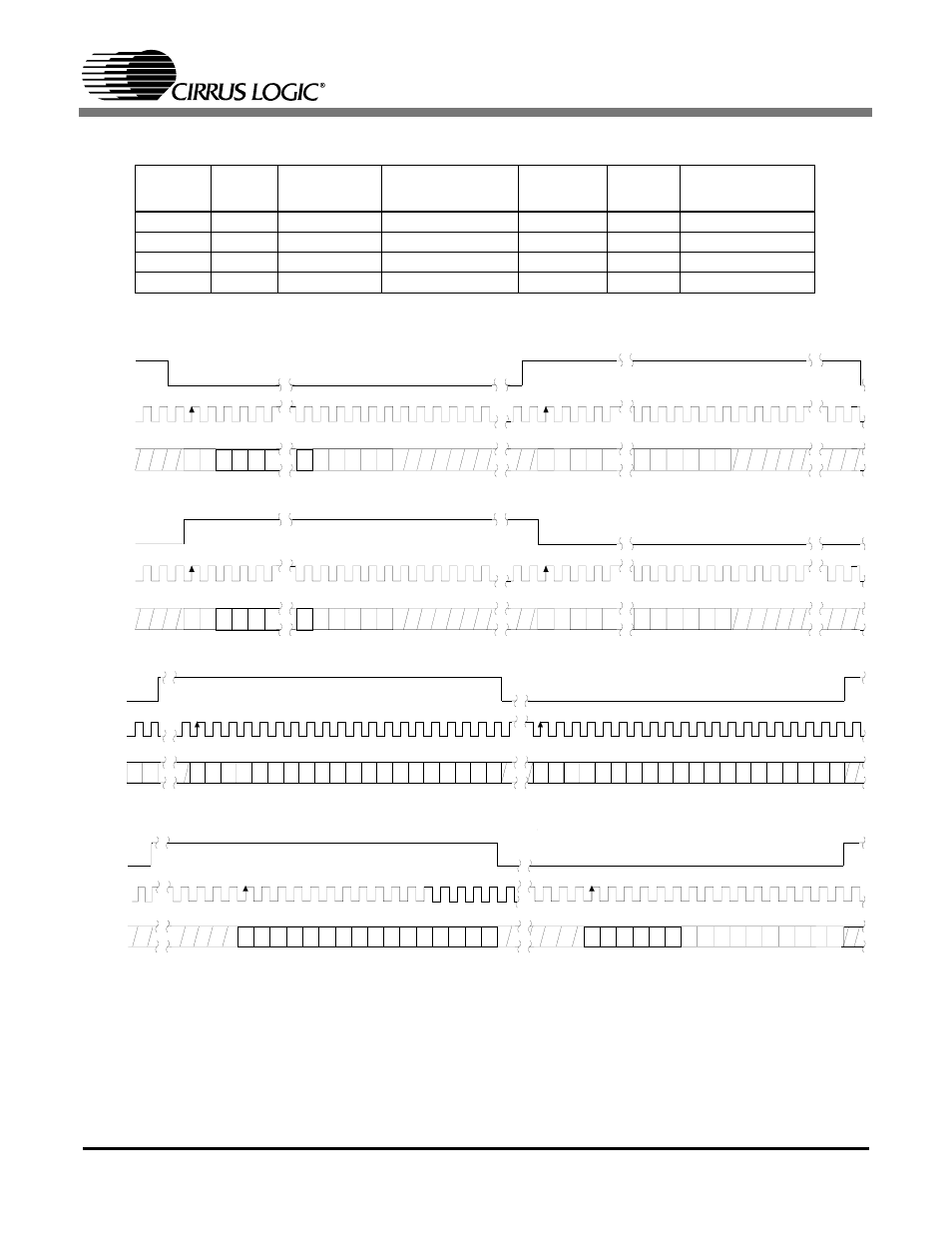

SDF[1:0]

LRCLK

Polarity

Data

Justification

Data Alignment

(MSB vs. LRCLK)

Data

Resolution

Timing

Diagram

Recommended

DAC/ADC

0 0

negative

left justified

1 SCLK delayed

CS4334/CS5331A

0 1

positive

left justified

not delayed

CS4335/CS5330A

1 0

positive

right justified

not delayed

20-bit Figure 19 CS4337/none

1 1

positive

right justified

not delayed

16-bit Figure 20 CS4338/none

Table 23. Serial Data Formats and Compatible DACs/ADC’s for the CS4205

LRCK

SCLK

Left Channel

Right Channel

SDATA

+3 +2 +1 LSB

+5 +4

MSB-1 -2 -3 -4 -5

+3 +2 +1 LSB

+5 +4

MSB-1 -2 -3 -4

Figure 17. Serial Data Format 0 (I

2

S)

LRCK

SCLK

Left Channel

Right Channel

SDATA

+3 +2 +1 LSB

+5 +4

MSB-1 -2 -3 -4 -5

+3 +2 +1 LSB

+5 +4

MSB-1 -2 -3 -4

Figure 18. Serial Data Format 1 (Left Justified)

LRCK

SCLK

Left Channel

Right Channel

SDATA

6 5 4 3 2 1 0

9 8 7

15 14 13 12 11 10

1 0

6 5 4 3 2 1 0

9 8 7

15 14 13 12 11 10

17 16

17 16

19 18

19 18

Figure 19. Serial Data Format 2 (Right Justified, 20-bit data)

LRCK

SCLK

Left Channel

Right Channel

SDATA

6

5

4

3

2

1

0

9

8 7

15 14 13 12 11 10

6

5

4

3 2

1

0

9

8

7

15 14 13 12 11 10

Figure 20. Serial Data Format 3 (Right Justified, 16-bit data)