GW Instek GPI-700A Series Programming Manual User Manual

Page 29

GPI/GPT SERIES PROGRAMMABLE EST

PROGRAMMER MANUAL

⎯ 55 ⎯

There are two status registers are included to the EST defined by IEEE-

488.1 and IEEE-488.2 standards.

z

Status Byte Register (SBR)

z

Standard Event Status Register (SESR)

Status Byte Register (SBR): The SBR (Table 6) summarizes the status of

all other registers and queues.

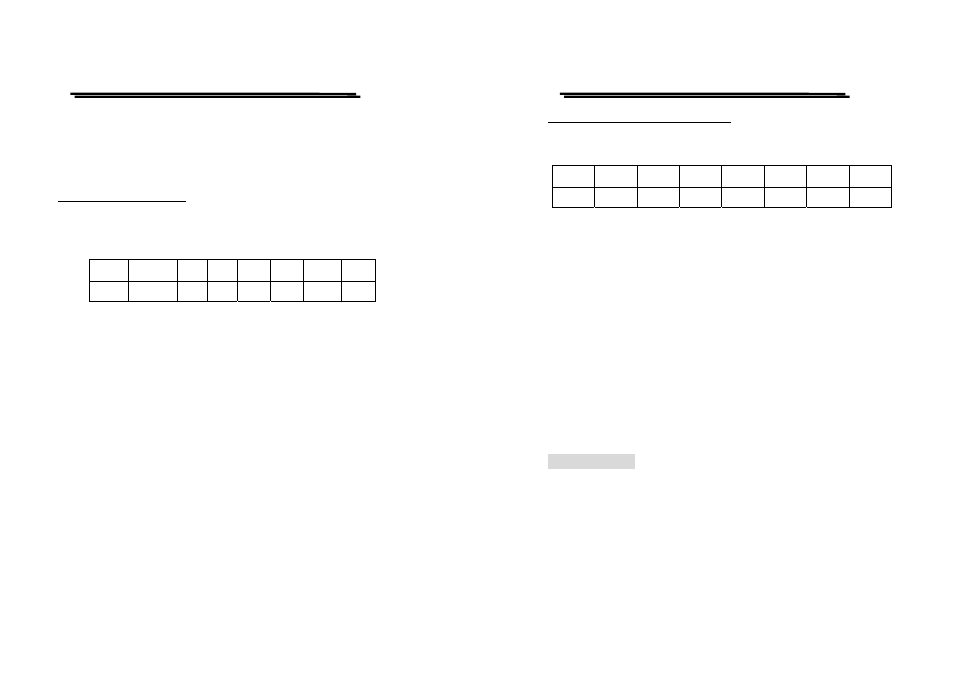

Table 6: Status Byte Register (SBR)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

OPER RQS/MSS ESB MAV QUES

E/E

NU

NU

The bit 0 and 1 are not used, so these bits are always zero. The bit 2

(Error and Event) indicates an error code is waiting to be read in the

Error Event Queue. The bit 3 (QUES, QUEStionable) is the summary bit

for the QESR (QUEStionable Event Status Register). When the bit is

high it indicates that status is enabled and present in the QUES. The bit 4

(MAV, Message Available) indicates that output is available in the

output queue. The bit 5 (ESB, Event Status Bit) is the summary bit for

the Standard Event Status Register (SESR). When the bit is high it

indicates that status is enabled and present in the SESR. The bit 6 (RQS,

Request Service) is obtained from a serial poll and shows that the EST

requests service from the GPIB controller. The bit 7 (OPER, OPERation)

is the summary bit for the OESR (OPERation EVENt STATus Register).

Use the serial poll or the *STB? Query to read the contents of the SBR.

The bits in the SBR are set and cleared depending on the contents of the

Standard Event Status Register (SESR), the Standard Event Status

Register (SESR), and the Output Queue.

GPI/GPT SERIES PROGRAMMABLE EST

PROGRAMMER MANUAL

⎯ 56 ⎯

Standard Event Status Register (SESR): Table 7 shows the SESR

Table 7: Standard Event Status Register (SESR)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

PON

URQ

CME

EXE

DDE

QYE

NU

OPC

The bit 0 (OPC, Operation Complete) shows that the operation is

completed. This bit is active when all pending operations are completed

following an *OPC command. The bit 1 is always zero. The bit 2 (QYE,

Query Error) indicates a command or query protocol error. The bit 3

(DDE, Device Error) shows that a device error occurred. The bit 4 (EXE,

Execution Error) shows that an error occurred while the EST was

executing a command or query. The bit 5 (CME, Command Error) shows

that an error occurred while the EST was parsing a command or query.

The bit 6 (USR, User Request) indicates the LOCAL button was pushed.

The bit 7 (PON, Power On) shows that the EST was powered on.

Use the *ESR? Query to read the SESR. Read the SESR and clear the bits

of the registers so that the register can accumulate information about new

events.

Enable Registers

The enable registers determine whether certain events are reported to the

Status Byte Register and SRQ. The EST has the following enable

registers.

z

Event Status Enable Register (ESER)

z

OPERation Enable Register

z

QUEStionable Enable Register

z

Service Request Enable Register (SRER)