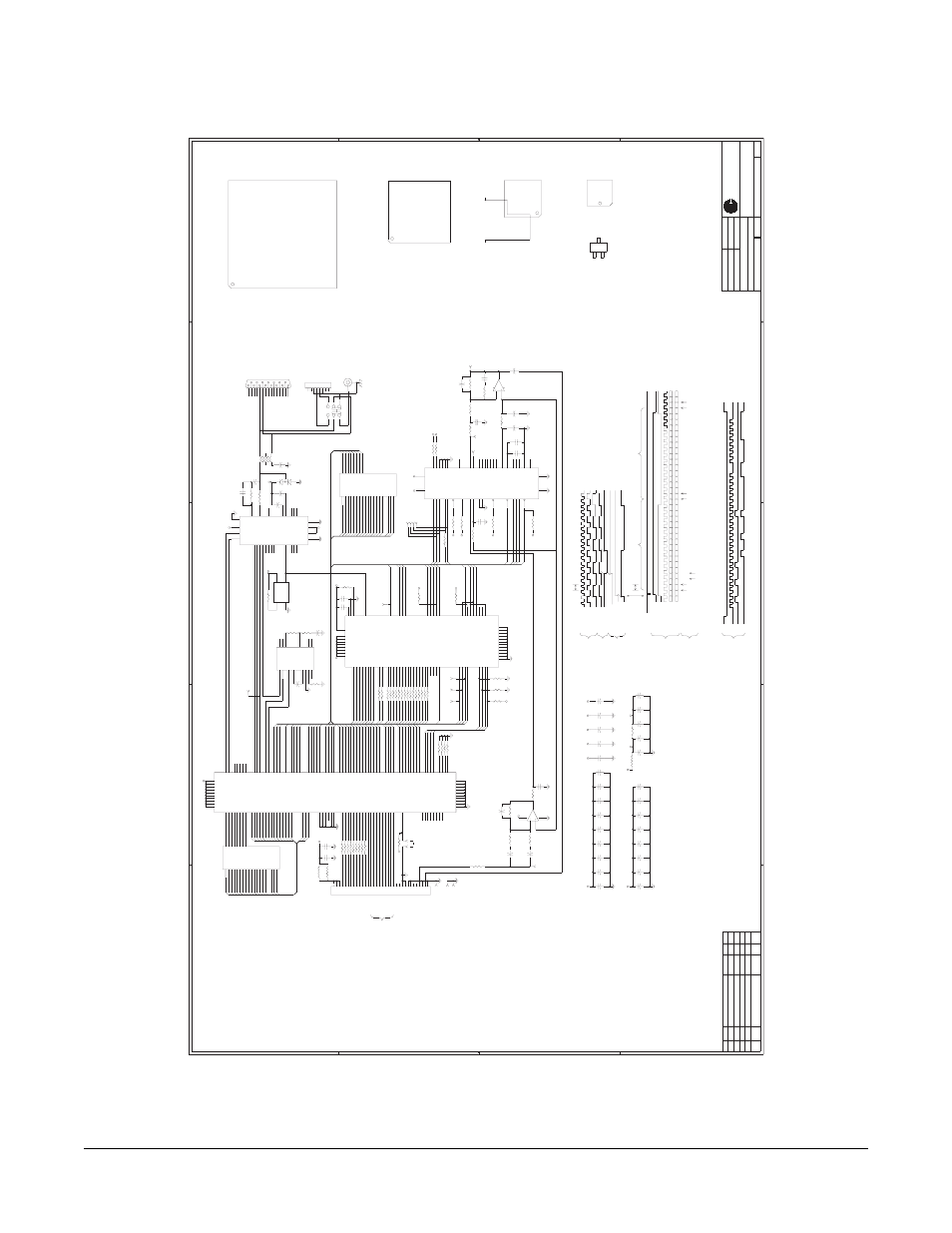

Schematic—com-20 communication pcb rev. c, Figure 3-20 – Clear-Com ICS-2003 User Manual

Page 73

Clear-Com Communication Systems

ICS-2003 Intercom Panel Instruction Manual

3 - 3 3

Figure 3-20:

Schematic—COM-20 Communication PCB Rev. C

A

A

B

B

C

C

D

D

E

E

4

4

3

3

2

2

1

1

B

C

2573

2581

Release to production

ADJUST

T

A

LK

GAIN;

R27

04-07-99

4/22/99

JEG

MAS

Schematic

COM-20 Digital Subscriber Station

710435 - SCH - D -

C

D

11

710435SC.DSN

J.E.Galbraith

0

4-07-99

-----------------------

REV

ECO#

DESCRIPTION

DA

TE

BY

CHK

CHK

DWN

APP

DA

TE

DA

TE

DA

TE

ORCAD P/N

SHEET

:

OF:

SCALE

SIZE

D

WG No.

REV

TITLE:

CLEAR-COM

INTERCOM SYSTEMS

®

TP23

CSDO

R62

1

.0K*

IC8A LMC6482

R47

220*

R75 0

C43

.1uF

(IC6)

R52

220*

D1

BA

V99

C38

.1uF

(IC2)

C39

.1uF

(IC6)

R63

1

.0K*

C47

.1uF

(IC5)

C51

47pF

C18

.47uF

+

L3

R53

220*

C10

.1uF

(IC6)

TP5

LOUT

T1

R33

4

.75K*

R40

0

R56

1

.0K*

R34

0

C19

10uF

+

TP14

R54

220*

R64

1

.0K*

R37

2.74K*

R35

0

J4

TP4

ROUT

C8

.1uF

C48

.1uF (IC7)

R65

1

.0K*

C7

100uF

+

R12

4

.75K*

IC7

CS4218

R36

0

R6

4.75K*

R43

1

.0K

IC2

62256

C42

.1uF

(IC6)

C20

.1uF

IC4

OSC 10.24MHz

IC1

710451

CPU Interface

JT

AG Port

(CPU Sel)

R67

1

.0K*

IC3 MT9171BP

R38

301*

R46

220*

R25

4.75K*

R3

392*

R1

4.75K*

R4

47.5*

C1

.0015uF

C4

.47uF

+

C17

.47uF

+

C5

.47uF

+

TP18

R68

1

.0K*

C26

.1uF

(IC3)

C2

.022uF

C6

.47uF

+

C28

.1uF

(IC1)

C29

.1uF

(IC1)

R39

3.24K*

C50

.1uF (IC8)

R69

1

.0K*

C3

.1uF

(IC9)

C36

.1uF

(IC1)

C31

.1uF

(IC1)

R9

4.75K*

C37

.1uF

(IC1)

J2

RJ-45

C32

.1uF

(IC1)

L1

TP24

C33

.1uF

(IC1)

R70

1

.0K*

IC9

74HCT4046

C24

10uF (IC7)

+

C34

.1uF

(IC1)

TP25

C35

.1uF

(IC1)

R71

1

.0K*

J5

BNC

TP27

R32

4.75K*

C27

.1uF

(IC4)

R72

1

.0K*

C9

.0033uF

R18

75.0K*

R22

0

C46

.1uF

(IC6)

R17

7.50K*

C1

1

4

7pF

R73

1.0K*

R16

0

IC5

62256

R44

4.75K*

TP46

S1

IC8B LMC6482

R55

604*

C52

.1uF

R24

4

.75K*

C41

.1uF

(IC6)

TP3

LISTEN

R41

4.75K*

R1

1

4

.75K*

C12

.0047uF

R74

1

.0K*

R48

220*

L2

C45

.1uF

(IC6)

R45

4.75K*

R58

1

.0K*

C14

.001uF*

R29

604*

C21

.33uF

R26

75.0K*

TP12

/F0

R19

604*

TP29

R49

220*

R13

4.75K*

C15

47pF

C13

.0047uF

R59

1

.0K*

TP30

C23

.0047uF

IC6

DSP56004

Serial Host Interface

Gen Purpose I/O

OnCE Serial

Serial Audio

Ext Memory

TP1

C16

.33uF

R50

220*

TP45

R30

2

.2

C44

.1uF

(IC6)

R28

4.99K*

R60

1

.0K*

C25

10uF (IC7)

+

TP20

SCLK

C22

.001uF*

R10

4

.75K*

C40

.1uF

(IC6)

C49

.1uF (IC7)

TP21

SSYNC

R51

220*

R42

4.75K*

R27

4.75K*

J1

DB-15M

TP22

CSDI

VCC

VCC

VCC

VCC

VCC

VCC

+5D0

VCC

VCC

+5A0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

+5D0

+5A0

+5A0

+5D0

+5D0

+5D0

+5D0

+5D0

+5D0

3

2

1

8

4

1

2

3

1

6

5

3

4

2

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

VA

18

VD

42

CLKIN

41

SSYNC

39

SCLK

38

/PDN

7

LIN1

21

RIN1

19

LIN2

22

RIN2

20

CDOUT

34

CDIN

33

/CCS

30

CCLK

29

/INT

32

/RESET

40

MF6

28

MF7

25

MF8

24

AGND

17

DGND

43

REFGND

16

REFBYP

15

REFBUF

14

SDOUT

37

SDIN

36

SMODE3

35

SMODE2

26

SMODE1

23

LOUT

10

ROUT

9

NC

44

NC

1

NC

2

NC

3

NC

4

NC

5

NC

6

NC

8

NC

11

NC

12

NC

13

DI1

27

DO1

31

A0

10

A1

9

A2

8

A3

7

A4

6

A5

5

A6

4

A7

3

A8

25

A9

24

A10

21

A1

1

23

A12

2

A13

26

A14

1

%%oCS%%o

20

%%oOE%%o

22

%%oWE%%o

27

D0

11

D1

12

D2

13

D3

15

D4

16

D5

17

D6

18

D7

19

OE

1

GND

2

OUT

3

VCC

4

VCC

7

VCC

19

VCC

22

VCC

42

GND

15

GND

30

GND

50

GND

54

%%oCPUIRQ%%o

107

CPUD0

106

CPUD1

105

CPUD2

104

CPUD3

103

CPUD4

101

CPUD5

100

CPUD6

99

CPUD7

98

/CE0

97

/AS--/CE1

96

/OE--R/W

95

/WEL--/RST

93

/RES--E

92

A2--A0

86

A3--A1

85

A4--A2

84

A5--A3

83

%%oRAMWE%%o

11

3

%%oRAMOE%%o

125

%%oRAMCS%%o

131

RAMA0

136

RAMA1

134

RAMA2

132

RAMA3

124

RAMA4

121

RAMA5

11

9

RAMA6

11

7

RAMA7

11

5

RAMA8

11

8

RAMA9

120

RAMA10

128

RAMD0

139

RAMD1

141

RAMD2

144

RAMD3

142

RAMD4

140

RAMD5

137

RAMD6

135

RAMD7

133

CODECSClk

74

CODECFSync

75

%%oCODECReset%%o

76

C16In

20

C8Out

73

%%oMCS%%o

59

%%oMRD%%o

61

%%oMWR%%o

60

MD0

62

MD1

63

MD2

64

MD3

65

MD4

67

MD5

68

MD6

69

MD7

70

A1--AS

89

MA4

43

MA2

40

MA3

41

TRSTB

71

TMS

72

TDI

38

TCK

109

STM

11

0

TDO

143

MODE

108

MA0

37

MA1

39

CDST

i

5

CDST

o

4

DST

i

3

DST

o

2

F0

6

GCLK/I

21

VCCIO

58

VCC

79

VCC

91

VCC

94

VCC

114

VCCIO

130

GND

66

GND

87

GND

102

GND

122

GND

126

GND

138

RAMA14

111

RAMA13

11

6

RAMA12

11

2

RAMA1

1

123

MA5

44

MA6

45

MA7

46

MA8

47

MA9

48

MA10

49

MA1

1

51

MA12

52

%%oDSPRES%%o

33

MODA/IRQA

34

MODB/IRQB

35

MODC/NMI

36

SPCLK

23

SPMISO

24

SPMOSI

25

%%oHA2%%o

26

HREQ

27

GPIO2

31

GPIO3

32

I

17

ACLK/I

18

ACLK/I

90

GPIO0

28

GPIO1

29

/C4Out

56

%%oBootRamCE%%o

57

MA13

53

MA14

55

DSI/OSO

8

DSCK/OS1

9

DSO

10

DR

11

Te

s

t6

127

Te

s

t7

129

Te

s

t5

88

n/c

12

n/c

13

n/c

14

n/c

16

n/c

1

Te

s

t0

77

Te

s

t1

78

Te

s

t2

80

Te

s

t3

81

Te

s

t4

82

CDSTO

13

CDSTI

12

VDD

28

MS2

5

DSTI

16

DST

O

15

F0/CLD

10

C4/TCK

19

F0O/RCK

17

REGC

9

PRECAN

23

OSC2

21

OSC1

22

MSO

8

MS1

7

TEST

26

VSS

14

LOUT

2

LIN

27

LOUT

DIS

24

VREF

4

VBIAS

3

NC

1

NC

6

NC

11

NC

18

NC

20

NC

25

1 2 3 4 5 6 7 8

CIN

3

VCOUT

4

SIN

14

CX

6

CX

7

INH

5

R1

11

R2

12

PP

1

P1

2

P2

13

VCOIN

9

DEMO

10

ZEN

15

A0

10

A1

9

A2

8

A3

7

A4

6

A5

5

A6

4

A7

3

A8

25

A9

24

A10

21

A1

1

23

A12

2

A13

26

A14

1

%%oCS%%o

20

%%oOE%%o

22

%%oWE%%o

27

D0

11

D1

12

D2

13

D3

15

D4

16

D5

17

D6

18

D7

19

1

2

3

4

5

6

5

6

7

MA0

25

MA1

24

MA2

23

MA3

22

MA4

20

MA5

19

MA6

18

MA7

16

MA8

14

MA9

13

MA10

12

MA1

1

11

MA12

7

MA13

5

MA15/MCS3

3

MA14

4

MD0

71

MD1

69

MD2

68

MD3

67

MD4

65

MD5

64

MD6

63

MD7

62

MA16/MCS2

80

MA17/MCS1

79

AGND

1

AGND

8

QGND

10

AGND

15

AGND

21

QGND

29

SGND

34

QGND

52

SGND

44

SGND

54

DGND

66

AVC

C

6

QVCC

9

AVC

C

17

QVCC

28

PVCC

33

SVCC

40

QVCC

53

SVCC

48

DVCC

70

DGND

72

PGND

31

EXT

AL

27

PCAP

32

%%oRESET%%o

36

MODA/IRQA

37

MODB/IRQB

38

MODC/NMI

39

%%oMRD%%o

77

%%oMWR%%o

78

%%oMCS0%%o

2

SCK/SCL

26

MISO/SDA

35

MOSI/HA0

41

SS/HA2

42

%%oHREQ%%o

43

GPIO0

76

GPIO1

75

GPIO2

74

GPIO3

73

PINIT

30

DSI/OS0

59

DSCK/OS1

60

DSO

58

%%oDR%%o

61

WSR

55

SCKR

51

SDI0

57

SDI1

56

WST

50

SCKT

49

SDO0

47

SDO1

46

SDO2

45

8

15

7

14

6

13

5

12

4

11

3

10

2

9

1

C10

C10

AD2

AD4 AD5

AD7

AD0

/IRQ

AD6

AD1

AD3

C4_DNIC

FR0A1

1

/FR0OE

FR0D2

/MCS /MWR

MD1

FR0A13

MA13

MA4

MD7

MA12

MD5

MD4

/FR0OE

FR0A5

FR0A12

MA8 MA9

MODA/IRQA

MODC/NMI

/BOOTRAMCE

/DSPRES

DSO

GPIO1

MODA/IRQA

FR0D7

MD0

MD4

FR0A9

MA4

FR0A8

MA1

1

FR0A0 FR0A1

MD4

/RST

FR0A2

FR0A14

FR0A1

1

MA12

HREQ

/BOOTRAMCE

MD2

MODC/NMI

MA10

DSCK/OS1

FR0A14

MA5

MD2

MA0

FR0A1

MD6

MD1

/MRD

MA6

FR0A7

MA14

FR0A8

FR0D0

FR0D5

FR0A3

MA1

/MCS

MA7

MA1

1

MA12

FR0A3

FR0D4

/MRD

MD3

AS

MA5

/MRD

MA5

MD7

HREQ

MA0

/FR0WE

FR0A0

MD2

MD7

MODB/IRQB

DSCK/OS1

MA7

MODB/IRQB

FR0A5

MA13

MD5

FR0A6

FR0D3

DST

o

MA1

MD1

MD3

FR0A4

MA14

FR0A9

FR0D1

MD5

/DSPRES

/FR0WE

MD3

MA6

FR0A10

MA9

FR0A4

MA6

MA1

1

/HA2

FR0A13

MD0

MD6

FR0A6

/CE0 /CE1

A1

MA4

FRM8KHz

/FR0CS

MA9

MD6

/MWR

R/W

FR0A7

GPIO1

DSO

MD0

MA10

MA10

FR0A2

E

A0

/FR0CS

FR0A10

FR0D6

DST

i

MA7

MA13

/MWR

MA8

MA0

GPIO3

MA14

FR0A12

MA8

A2 A3

C16

MA1

/C4

DSI/OSO

/DR

/DR

DSI/OSO

/TW

CDST

i

CDST

o

/HA2

TW

MA3

MA2

MA2 MA3

MA3

MA2

GPIO3 FRM8KHz

/F0

SCLK

CSDI

SPCLK

GPIO0

C8

SPMOSI

SPCLK

GPIO0

SPMOSI

SPMISO

VREF

C8

SSYNC

/CODECRES

CSDO

GPIO0

SCLK

SSYNC

SSYNC

SPMOSI

SPMISO

CSDI

SCLK

/CODECRES

VREF

SPMISO

SPCLK

CSDO

PC Board #170264

Boot RAM

Filtered CODEC Power

DSP56004

COM3A

FRAMER

OP

Amp

LSB

MSB

LSB

M

SB

Right W

o

rd Bits

Left W

o

rd Bits

LSB

M

SB

DSP

Serial

Audio Interface to CODEC timing

CSDI -

TP22

CSDO -

TP23

PLL

MF=5

DSP

Clock=51.2 MHz

18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

132

131

130

129

128

127

126

125

124

123

122

121

120

52

53

108 107 106 105 104 103 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86

51

85 84

119

118

117

TQFP

Package

Shown 4-times life size

133

134

135

136

137

138

139

140

141

142

143

144

116

115

114

113

112

111

110

109

10 11

1 2 3 4 5 6 7 8 9

12 13 14 15 16 17

37

38

39

40

41

42

43

44

45

46

47

48

49

50

73

74

75

76

77

78

79

80

81

82

83

GND

GND

GND

GND

GND

GND

VCC

VCC

VCC

VCC

VCC

VCC

GND

GND

GND

GND

VCCIO

VCC

VCC

VCCIO

GCLK/1

I

I

I

I

Pinout for 144-Pin

710451 FPGA

RAMA8

RAMA6

RAMA9

RAMA5

RAMA11

RAMA4

/RAMOE

RAMA3

RAMA10

RAMA2

/RAMCS

RAMA1

RAMD7

RAMD6

RAMA0

RAMD5

RAMD0

RAMD4

RAMD1

RAMD3

RAMD2

n/c

DST

o

DST

i

CDST

i

CDST

o

F0

C16In

TDI

ACLK/I

ACLK/I

GCLK/1

TDO

TMS

TRSTB

TCK

STM

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

/MCS0

/MWR

/MRD

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

C8

SCLK

FSYNC

CPUA3

CPUA2

CPUA1

CPUA0

CPUA4

CPUEClk

/CPURES

CPUR/W

CPUCE1

CPUCE0

CPUD7

CPUD6

CPUD5

CPUD4

CPUD3

CPUD2

CPUD1

CPUD0

/CPUIRQ

MODE

n/c n/c

n/c

/CODECRES

MODA/IRQA

DSPRES

MODB/IRQB MODC/IRQC

SPCLK

SPMISO SPMOSI

HA2

HREQ

GPIO2

RAMA7

RAMA13

RAMA12

/RAMWE

Test7

/C4Out

n/c

GPIO3

RAMA14

n/c

Test6

MA13

MA14

Te

s

t3

Te

s

t2

Te

s

t1

Te

s

t0

n/c

(CODEC)

(DNIC)

(RAM)

(DSP/EPROM)

(J4)

GPIO1

GPIO0

DSI/OSO

DSCK/OS1

DSO

DR

Te

s

t4

Te

s

t5

(gnd)

gnd gnd

AGND

DGND

/HREQ

2

Vi

e

w

16

14

8

4

11

40

30

33

21

25

51

55

59

46

50

69

65

61

76

80

AV

C

C

MA15/MCS3

MA6

MA2

EXTAL

SCKT

MA16/MCAS

SVCC

MODA/IRQA

SDI1

DSCK/OS1

Shown 4-times

PGND

MA1

1

MD5

MD1

GPIO1

AGND

SVCC

/SS/HA2

MA17/MRAS

To

p

3

20

18

9

5

1

39

28

32

36

24

43

54

58

45

49

70

66

62

75

79

AV

C

C

/MSC0

MA7

MA3

SCK/SCL

SDO0

life size

SGND

/RESET

WSR

DSI/OS0

QGND

MA12

MD6

MD2

GPIO2

QVCC

SGND

MOSI/HA0

/MWR

SOT

-23

17

15

12

6

2

38

27

31

35

23

42

53

57

44

48

71

67

63

74

78

QGND

DVCC

MA8

MA4

MA0

SDO2

Pinout for 80-Pin

QGND

MISO/SDA

SCKR

QVCC

MA13

DSO

MD7

MD3

GPIO3

AGND

PCAP

MODC/NMI

/MRD

1

10

19

13

7

3

37

26

29

34

22

41

52

56

60

47

72

68

64

73

77

DSP560004

AGND

DGND

MA9

MA5

MA1

SDO1

BA

V99

QVCC

PINIT

WST

SGND

MA14

MODB/IRQB

SDI0

QFP

Package

PVCC

MA10

DR

MD4

MD0

GPIO0

EXT

AL=10.24 MHz

VA

DO1

DI1

SMODE1

LIN2

Digital

1

5

9

15

19

34

38

42

24

28

32

/RESET

Ground

SDIN

n/c

n/c

n/c

AGND

/INT

MF6

LIN1

MF8

LOUT

11

4

8

14

18

22

37

41

23

27

31

CLKIN

Analog

SDOUT

Region

REFGND

CDIN

CCLK

n/c

n/c

RIN2

MF7

ROUT

10

3

7

13

17

21

36

40

44

26

30

VD

Plane

SCLK

Region

REFBYP

CDOUT

/CCS

n/c

n/c

n/c

RIN1

SMODE2

/PDN

2

6

12

16

20

35

39

43

25

29

33

DGND

Ground

SSYNC

Plane

REFBUF

SMODE3

n/c

n/c

n/c

CS4218

life size

44-Pin TQFP

Shown 3-times

Package

Pinout for

23

13

28

9

Package

26

7

Shown 2-times

18

24

5

16

11

28-Pin PLCC

14

MT8971BP

life size

12

Pinout for

27

17

8

25

15

6

10

4

3

2

1

20

21

19

22

n/c

n/c

n/c

n/c

n/c

n/c

LOUT VBias VRef

TEST

LIN

VDD

/F0o DST

i/Di

DST

o/Do

VSS CDST

o/CDo

CDST

i/CDi

MS2

MS1

MS0

RegC

/F0/CLD

LOUT DIS

Precan

OSC1

OSC2

/C4/TCK

"T

ALK_AUDIO" input level is limited in the panel to +6dBu.

Input

T

a

lk amplifier gain is set to -36dB.

CODEC input clipping level is +2dBu (REFBUF voltage + 1.0V

rms).

CODEC output attenuation is set to -13.5dB.

CODEC output Listen amplifier gain is set to +9dB.

"LISTEN_AUDIO" level should be the same as "T

ALK_AUDIO".

The MA

TRIX+III sets a +10dBu headroom above maximum audio level.

Note:

T

a

lk and Listen amplifier gain issues.

Phase Locked Loop

C16 - IC9,Pin4

/C4 - IC9,Pin3

C8/CLKIN - IC7,Pin41

DNIC/FPGA/PLL

clock timing

LSB

MSB

LSB

M

SB

Ref, SSYNC

- 2-Wire Data

+ 2-Wire Data

+ 2-Wire Data

FOR COAX

CGND

FOR RJ-45

- 2-Wire Data

C16 Period = 61 nS

SCLK Period = 977 nS

PLL/FPGA

C4_DNIC - IC9,Pin14

\\\

\\\

\\\

\\\

/F0 (8KHz) -

TP12

\\\

DNIC

Next Frame

FPGA/DSP/CODEC

FRM8KHz/Sync -

TP27

SSYNC (32KHz) -

TP21

SCLK (1MHz) -

TP20

(Second of four SSYNC pulses)

(Jitter)

"0 dBu" reference level is 0.775 V

rms (impedence not specified).

COM-20

OPTIONAL

PIN

ASSIGNEMNTS

/RES--E

LISTEN_AUDIO

RAM

VCC

/AD7

REC

A4--A2

DGND

/AD1

VCC

AGND

/AD0

+12A

/AD3

/AS--/CE1 /OE--R/W

/WEL--/RST

/AD4

AGND

-12A

XMIT

AGND

A5--A3

DGND

T

A

LK_AUDIO

/CE0

VCC

A2--A0

/AD2

AGND

/AD6

/IRQ

A3--A1

/AD5

A1--AS

/F0 (8KHz) -

TP12

SCLK (1MHz) -

TP20

SSYNC (32KHz) -

TP21

Sync on /F0 or rising edge of FRM8KHz.

FRM8KHz/Sync -

TP27

FPGA/DSP/CODEC

DNIC

Left Rcv ISR

Left Xmit ISR

Right Rcv ISR

Right Xmit ISR (Sync and restart ISR states)

Right Xmit ISR (next ISR state)

Right Rcv ISR

W

rite and Read FRAMER data.

Update ISR buf

fers

DSP

program -

TP1

Interrupt ISRs

DSP

Program

Audio Conversion \\\ W

a

it for next FRM8KHz/Right Xmit ISR sync

T

a

lk Amplifier

Gain Adjust,

R27

R26,C22=75uS Preemphasis

Boot CE

S/W

Sync

DSP

Reset

Note:

TP1 indicates the DSP

internal program activity (including interrupt ISRs). Sync on either

TP12 or rising edge of

TP27.

Gain

Adjust, R17 +600 Ohms

Short

TP23

loop-back

R18,C14=75uS Deemphasis

SM4 Mode

to TP22

for

TS 1

Listen Amplifier

Slave 32 BPF

32 BPF

CODEC audio

as a two pin jumper jack to

In for: ISC2003

ICS21

10

Out for: ICS52

ICS62 ICS92 ICS102 ICS1502

select processor type.

TP30 and

TP45 are installed

CODEC nominal input gain is set to +12dB and can be adjusted between 0dB and +22.5dB.

The COM20 input and output gains are set to match those of a COM10 4-wire interface in a typical station.

GPIO0

SPCLK

SPMOSI

SPMISO

DSP

Serial Command Interface to CODEC timing (T

ypical

T

ransaction)

Sync on falling edge of GPIO0.

ADV

DI1

V

er

1

A

DV

DI1

MSK

A3

A0

G3

Mute

DO1

DSP/CODEC

G2

G1

G0

A4

A2

A1

(Interrupt Mask=1, Mute is of

f, Gain (G(3..0)) is 8 (+12dB),

Attenuation (A(4..0)) is 9 (-13.5dB), Mute=0, DO1=0,

ADV=1, DI1=1.

)

--

--