Max3301e usb on-the-go transceiver and charge pump, Table 9. v, Control logic – Rainbow Electronics MAX3301E User Manual

Page 24

MAX3301E

USB On-the-Go Transceiver and Charge Pump

24

______________________________________________________________________________________

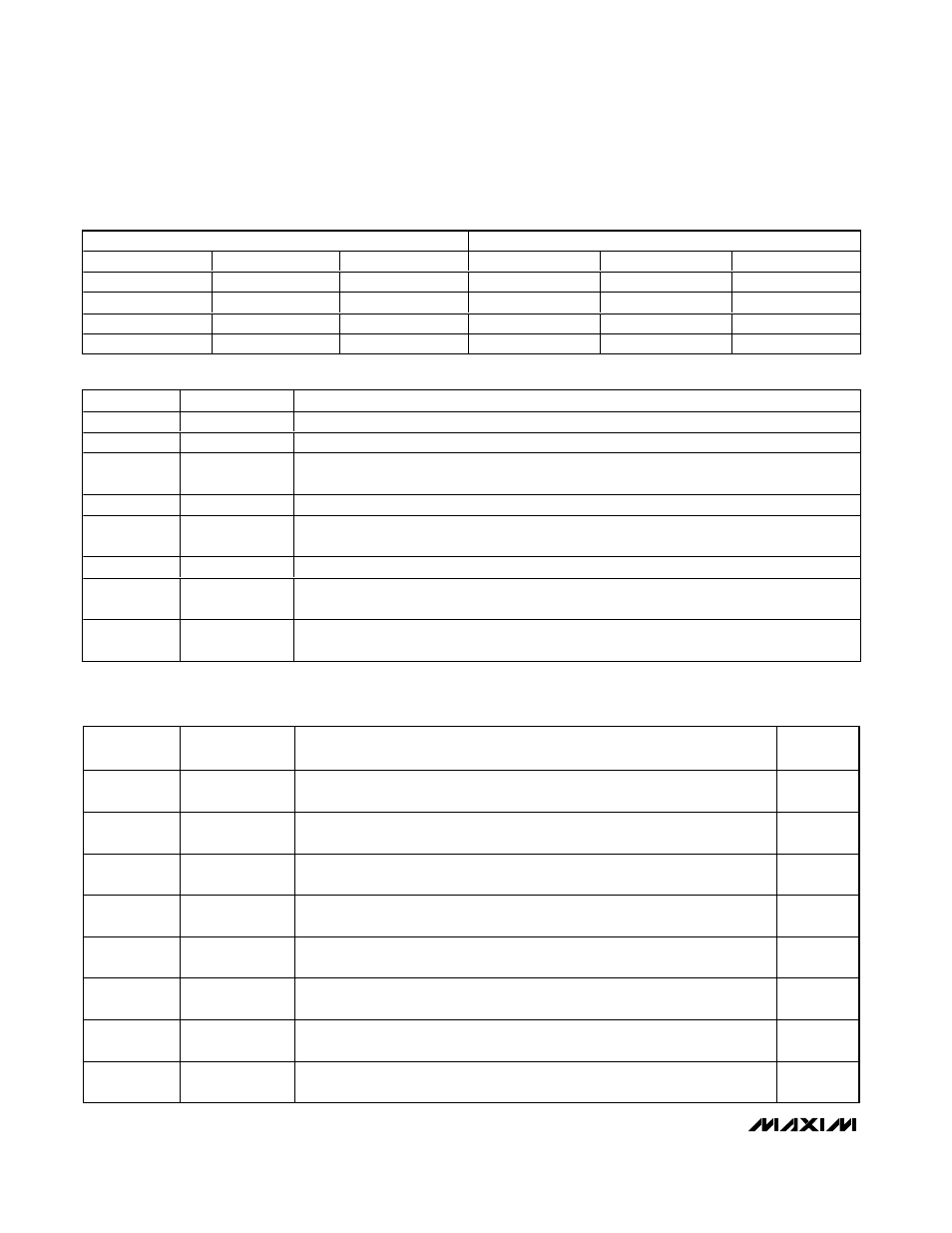

SET COMMAND (ADDRESS 06h)

BEHAVIOR OF MAX3301E

vbus_drv

vbus_dischrg

vbus_chrg

vbus_drv

vbus_dischrg

vbus_chrg

1

X

X

1

0

0

0

1

X

0

1

0

0

0

1

0

0

1

0

0

0

Not affected

Not affected

Not affected

Table 9. V

BUS

Control Logic

BIT NUMBER

SYMBOL

CONTENTS

0

vbus_vld

Logic 1 if V

BUS

> V

BUS

valid comparator threshold.

1

sess_vld

Logic 1 if V

BUS

> session valid comparator threshold.

2

dp_hi

Logic 1 if V

D+

> dp_hi comparator threshold (D+ assertion during data line pulsing through

SRP method).

3

id_gnd

Logic 1 if V

ID_IN

< 0.1 x V

CC

.

4

dm_hi

Logic 1 if V

D-

> dm_hi comparator threshold (D- assertion during data line pulsing through SRP

method).

5

id_float

Logic 1 if V

ID_IN

> 0.9 x V

CC

.

6

bdis_acon

Logic 1 if bdis_acon_en = 1 and the MAX3301E asserts dp_pullup after detecting a B device

disconnect during HNP.

7

cr_int_sess_end

Log i c 1 i f V

BU S

< sess_end com p ar ator thr eshol d , or i f V

D +

> cr _i nt com p ar ator thr eshol d ( 0.4V to

0.6V ) , d ep end i ng on the val ue of i nt_sour ce ( b i t 5 of sp eci al - functi on r eg i ster 1, see Tab l e 14) .

Table 10. Interrupt Source Register (Address 08h is Read Only)

BIT NUMBER

SYMBOL

CONTENTS

VALUE AT

POWER-UP

0

vbus_vld

vb us_vl d asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate

i nter r up t- hi g h or i nter r up t l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

1

sess_vld

sess_vl d asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate

i nter r up t- hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

2

dp_hi

d p _hi asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate i nter r up t-

hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

3

id_gnd

i d _g nd asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate i nter r up t-

hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

4

dm_hi

d m _hi asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate i nter r up t-

hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

5

id_float

i d _fl oat asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate i nter r up t-

hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

6

bdis_acon

b d i s_acon asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate

i nter r up t- hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

7

cr_int_sess_end

cr _i nt_sess_end asser ts i f a tr ansi ti on occur s on thi s cond i ti on and the ap p r op r i ate

i nter r up t- hi g h or i nter r up t- l ow enab l e b i t i s set. S ee Tab l es 10, 12, and 13.

0

Table 11. Interrupt Latch Register Description (Write to Address 0Ah to Set, Write to

Address 0Bh to Clear)