Enhanced cpu – Rainbow Electronics AT89LP216 User Manual

Page 9

9

3621A–MICRO–6/06

AT89LP216 [Preliminary]

8.

Enhanced CPU

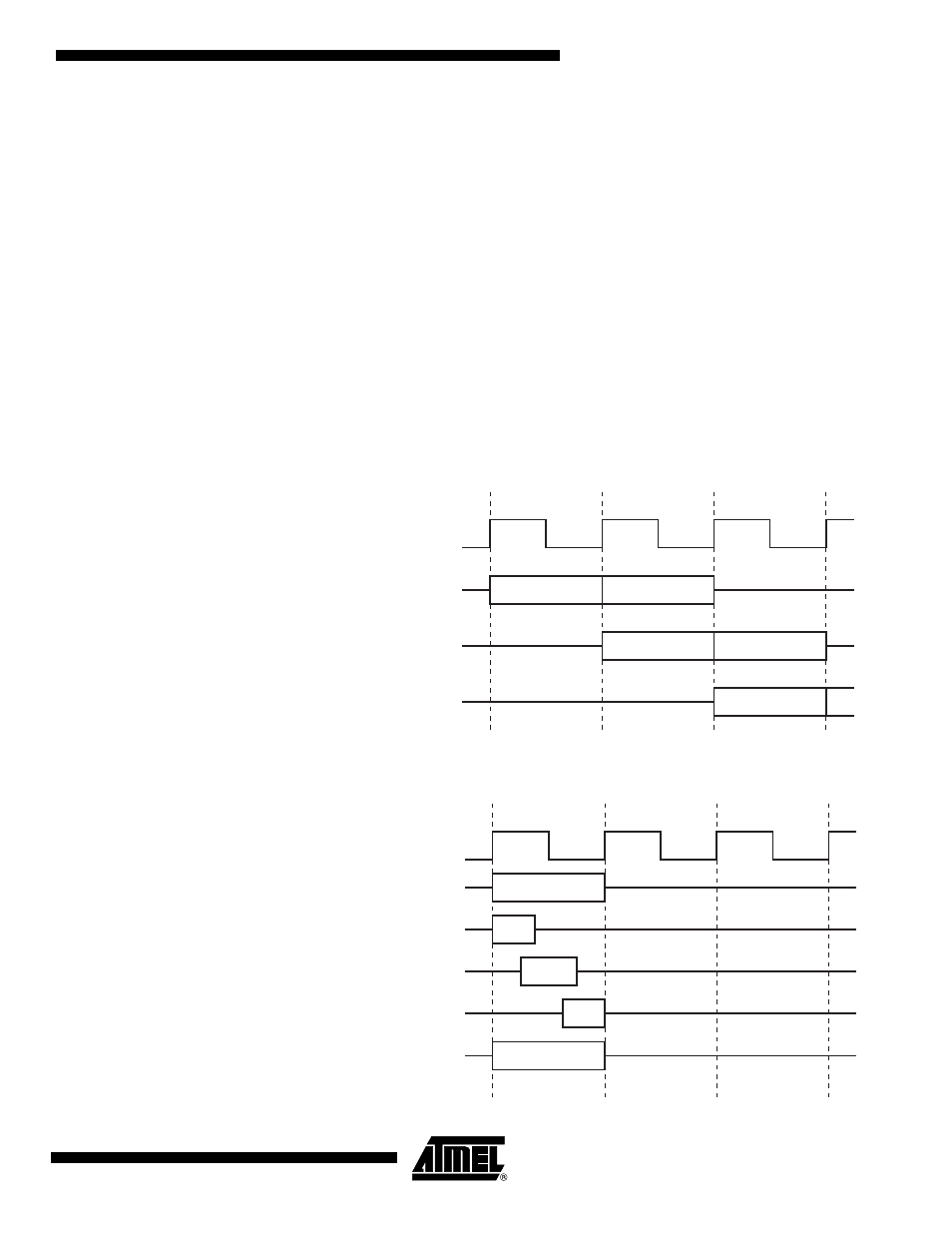

The AT89LP216 uses an enhanced 8051 CPU that runs at 6 to 12 times the speed of standard

8051 devices (or 3 to 6 times the speed of X2 8051 devices). The increase in performance is

due to two factors. First, the CPU fetches one instruction byte from the code memory every clock

cycle. Second, the CPU uses a simple two-stage pipeline to fetch and execute instructions in

parallel. This basic pipelining concept allows the CPU to obtain up to 1 MIPS per MHz. A simple

example is shown in

.

The MCS-51 instruction set allows for instructions of variable length from 1 to 3 bytes. In a sin-

gle-clock-per-byte-fetch system this means each instruction takes at least as many clocks as it

has bytes to execute. The majority of instructions in the AT89LP216 follow this rule: the instruc-

tion execution time in clock cycles equals the number of bytes per instruction with a

few exceptions. Branches and Calls require an additional cycle to compute the target address

and some other complex instructions require multiple cycles.

See “Instruction Set Summary” on

for more detailed information on individual instructions.

examples of 1- and 2-byte instructions.

Figure 8-1.

Parallel Instruction Fetches and Executions

Figure 8-2.

Single-cycle ALU Operation (Example: INC R0)

System Clock

n

th

Instruction

(n+1)

th

Instruction

Fetch

Execute

Fetch

Execute

Fetch

T

n

T

n+1

T

n+2

(n+2)

th

Instruction

System Clock

Total Execution Time

Register Operand Fetch

T

1

T

2

T

3

ALU Operation Execute

Result Write Back

Fetch Next Instruction