Reset, 1 power-on reset – Rainbow Electronics AT89LP216 User Manual

Page 12

12

3621A–MICRO–6/06

AT89LP216 [Preliminary]

10. Reset

During reset, all I/O Registers are set to their initial values, the port pins are tristated, and the

program starts execution from the Reset Vector, 0000H. The AT89LP216 has five sources of

reset: power-on reset, brown-out reset, external reset, watchdog reset, and software reset.

10.1

Power-on Reset

A Power-on Reset (POR) is generated by an on-chip detection circuit. The detection level is

nominally 1.4V. The POR is activated whenever V

CC

is below the detection level. The POR cir-

cuit can be used to trigger the start-up reset or to detect a supply voltage failure in devices

without a brown-out detector. The POR circuit ensures that the device is reset from power-on. A

power-on sequence is shown in

. When V

CC

reaches the Power-on

Reset threshold voltage V

POR

, an initialization sequence lasting t

POR

is started. When the initial-

ization sequence completes, the start-up timer determines how long the device is kept in POR

after V

CC

rise. The POR signal is activated again, without any delay, when V

CC

falls below the

POR threshold level. A Power-on Reset (i.e. a cold reset) will set the POF flag in PCON. The

internally generated reset can be extended beyond the power-on period by holding the RST pin

low longer than the time-out.

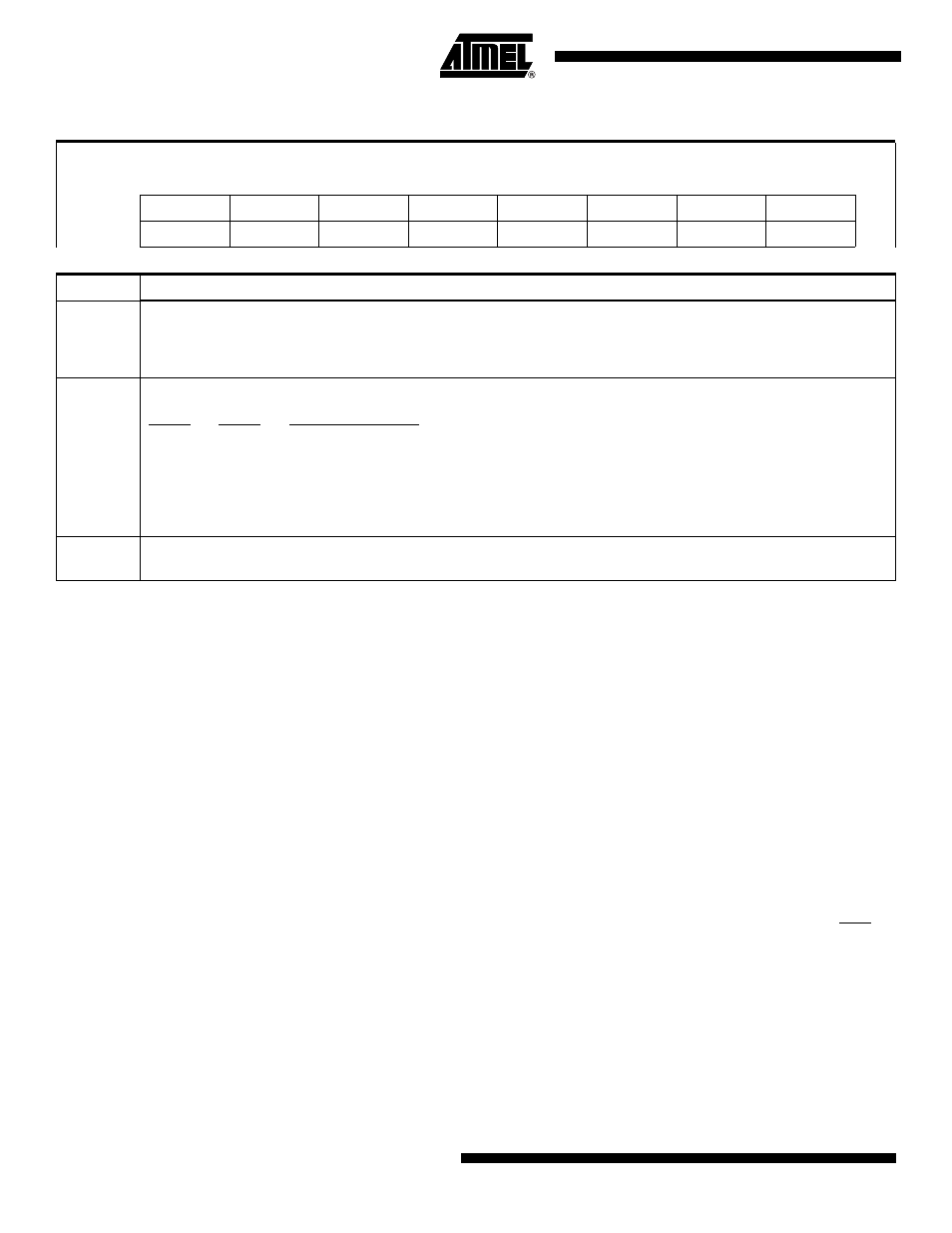

Table 9-2.

CLKREG

– Clock Control Register

CLKREG = 8FH

Reset Value = 0000 0000B

Not Bit Addressable

TPS3

TPS2

TPS1

TPS0

–

CDV1

CDV0

COE

Bit

7

6

5

4

3

2

1

0

Symbol

Function

TPS3

TPS2

TPS1

TPS0

Timer Prescaler. The Timer Prescaler selects the time base for Timer 0, Timer 1 and the Watchdog Timer. The prescaler

is implemented as a 4-bit binary down counter. When the counter reaches zero it is reloaded with the value stored in the

TPS bits to give a division ratio between 1 and 16. By default the timers will count every clock cycles (TPS = 0000B). To

configure the timers to count at a standard 8051 rate of once every 12 clock cycles, TPS should be set to 1011B.

CDV1

CDV0

Clock Out Division. Determines the frequency of the clock output relative to the system clock.

CDIV1

CDIV0

Clock Out Frequency

0

0

f/2

0

1

f/4

1

0

f/8

1

1

f/16

COE

Clock Out Enable. Set COE to output a divided version of the system clock on XTAL2 (P3.3). The internal RC oscillator

or external clock source must be selected in order to use this feature.