Analog comparator, 1 comparator interrupt with debouncing – Rainbow Electronics AT89LP216 User Manual

Page 55

55

3621A–MICRO–6/06

AT89LP216 [Preliminary]

19. Analog Comparator

A single analog comparator is provided on the AT89LP216. The analog comparator has the fol-

lowing features:

• Comparator Output Flag and Interrupt

• Selectable Interrupt Condition

– High- or Low-level

– Rising- or Falling-edge

– Output Toggle

• Hardware Debouncing Modes

Comparator operation is such that the output is a logic “1” when the positive input AIN0 (P1.0]) is

greater than the negative input AIN1 (P1.1). Otherwise the output is a zero. Setting the CEN bit

in ACSR enables the comparator. When the comparator is first enabled, the comparator output

and interrupt flag are not guaranteed to be stable for 10 µs. The corresponding comparator inter-

rupt should not be enabled during that time, and the comparator interrupt flag must be cleared

before the interrupt is enabled in order to prevent an immediate interrupt service. Before

enabling the comparator the analog inputs should be tristated by putting P1.0 and P1.1 into

input-only mode. See

“Port 1 Analog Functions” on page 25

The comparator may be configured to cause an interrupt under a variety of output value condi-

tions by setting the CM bits in ACSR. The comparator interrupt flag CF in ACSR is set whenever

the comparator output matches the condition specified by CM. The flag may be polled by soft-

ware or may be used to generate an interrupt and must be cleared by software.

19.1

Comparator Interrupt with Debouncing

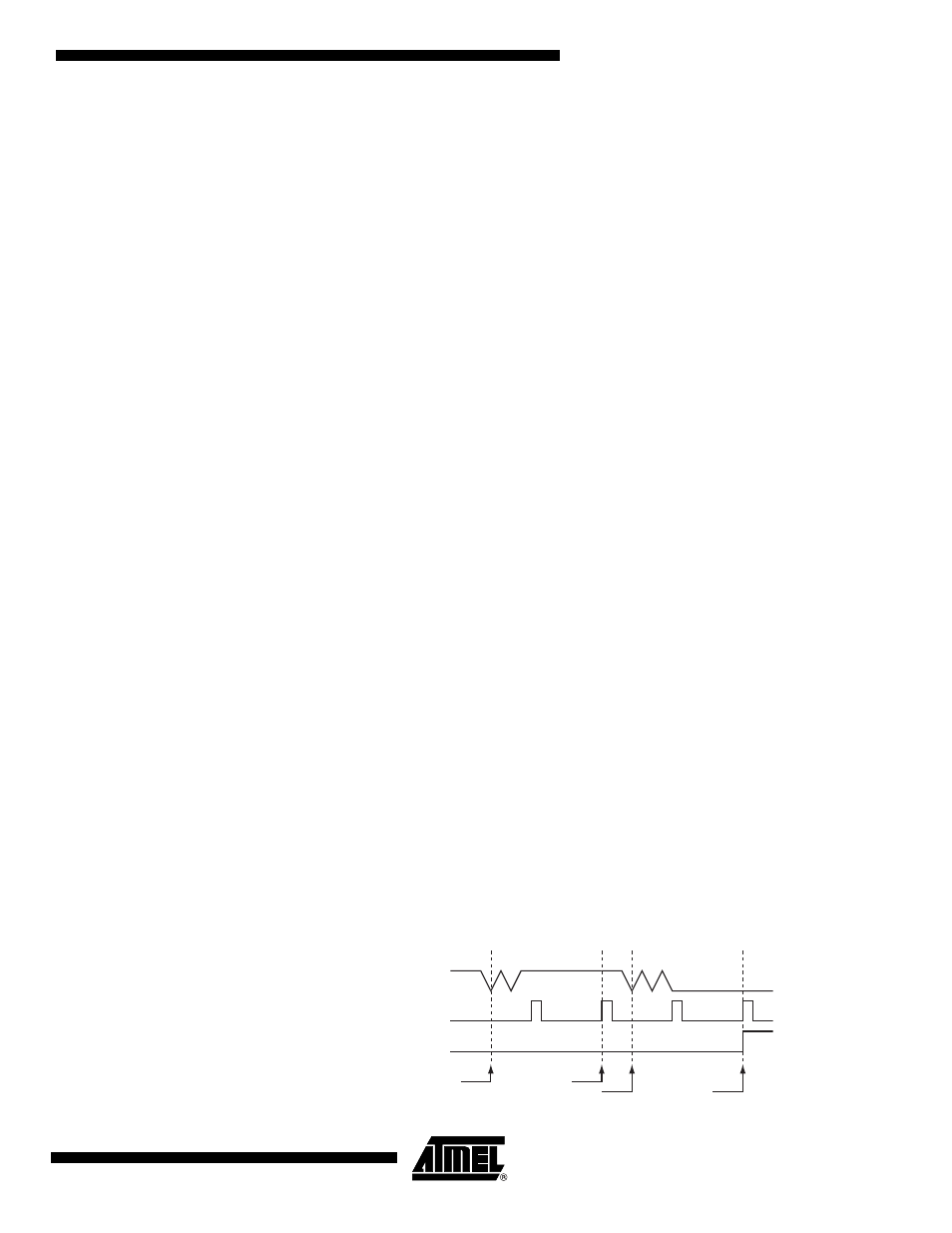

The comparator output is sampled every clock cycle. The conditions on the analog inputs may

be such that the comparator output will toggle excessively. This is especially true if applying slow

moving analog inputs. Three debouncing modes are provided to filter out this noise. In debounc-

ing mode, the comparator uses Timer 1 to modulate its sampling time. When a relevant

transition occurs, the comparator waits until two Timer 1 overflows have occurred before resam-

pling the output. If the new sample agrees with the expected value, CF is set. Otherwise, the

event is ignored. The filter may be tuned by adjusting the time-out period of Timer 1. Because

Timer 1 is free running, the debouncer must wait for two overflows to guarantee that the sam-

pling delay is at least 1 time-out period. Therefore, after the initial edge event, the interrupt may

occur between 1 and 2 time-out periods later. See

.

By default the comparator is disabled during Idle mode. To allow the comparator to function dur-

ing Idle, the CIDL bit is ACSR must be set. When CIDL is set, the comparator can be used to

wake-up the CPU from Idle if the comparator interrupt is enabled. The comparator is always dis-

abled during Power-down mode.

Figure 19-1. Negative Edge with Debouncing Example

Comparator Out

Timer 1 Overflow

CF

Start

Compare

Start Compare