4 status register, 5 data polling, 6 flash security – Rainbow Electronics AT89LP216 User Manual

Page 70

70

3621A–MICRO–6/06

AT89LP216 [Preliminary]

23.4

Status Register

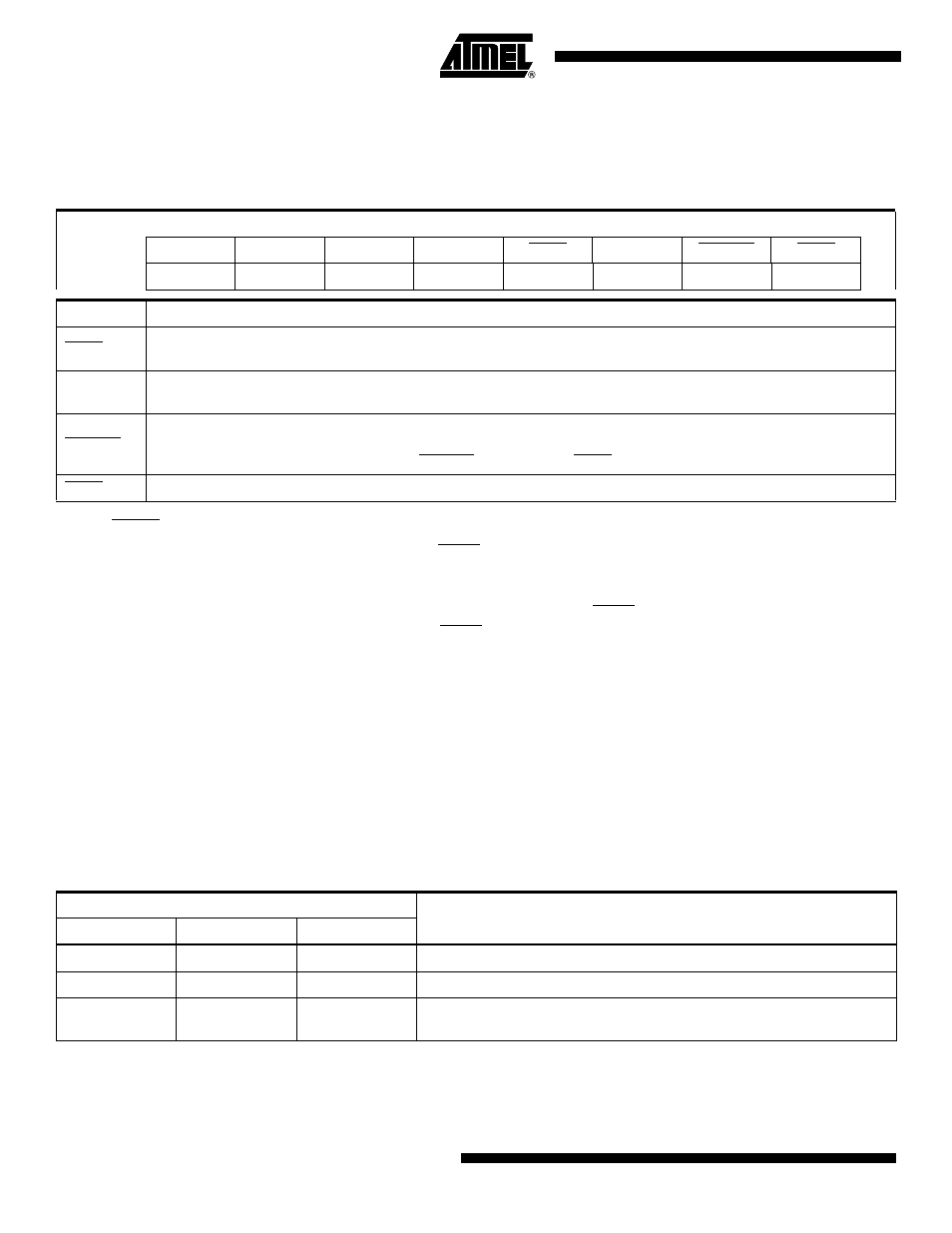

The current state of the memory may be accessed by reading the status register. The status reg-

ister is shown in

.

23.5

DATA Polling

The AT89LP216 implements DATA polling to indicate the end of a programming cycle. While the

device is busy, any attempted read of the last byte written will return the data byte with the MSB

complemented. Once the programming cycle has completed, the true value will be accessible.

During Erase the data is assumed to be FFH and DATA polling will return 7FH. When writing

multiple bytes in a page, the DATA value will be the last data byte loaded before programming

begins, not the written byte with the highest physical address within the page.

23.6

Flash Security

The AT89LP216 provides two Lock Bits for Flash Code Memory security. Lock bits can be left

unprogrammed (FFh) or programmed (00h) to obtain the protection levels listed in

.

Lock bits can only be erased (set to FFh) by Chip Erase. Lock bit mode 2 disables programming

of all memory spaces, including the User Signature Array and User Configuration Fuses. User

fuses must be programmed before enabling Lock bit mode 2 or 3. Lock bit mode 3 implemented

mode 2 and also blocks reads from the code memory; however, reads of the User Signature

Array, Atmel Signature Array, and User Configuration Fuses are still allowed.

Table 23-3.

Status

Register

–

–

–

–

LOAD

SUCCESS

WRTINH

BUSY

Bit

7

6

5

4

3

2

1

0

Symbol

Function

LOAD

Load flag. Cleared low by the load page buffer command and set high by the next memory write. This flag signals that

the page buffer was previously loaded with data by the load page buffer command.

SUCCESS

Success flag. Cleared low at the start of a programming cycle and will only be set high if the programming cycle

completes without interruption from the brownout detector.

WRTINH

Write Inhibit flag. Cleared low by the brownout detector (BOD) whenever programming is inhibited due to V

CC

falling

below the minimum required programming voltage. If a BOD episode occurs during programming, the SUCCESS flag

will remain low after the cycle is complete. WRTINH low also forces BUSY low.

BUSY

Busy flag. Cleared low whenever the memory is busy programming or if write is currently inhibited.

Table 23-4.

Lock Bit Protection Modes

Program Lock Bits (by address)

Mode

00h

01h

Protection Mode

1

FFh

FFh

No program lock features

2

00h

FFh

Further programming of the Flash is disabled

3

00h

00h

Further programming of the Flash is disabled and verify (read) is also

disabled; OCD is disabled