Rainbow Electronics AT89LP216 User Manual

Page 75

75

3621A–MICRO–6/06

AT89LP216 [Preliminary]

23.8.6

Timing Parameters

The timing parameters for

.

Note:

1. t

SCK

is independent of t

CLCL

.

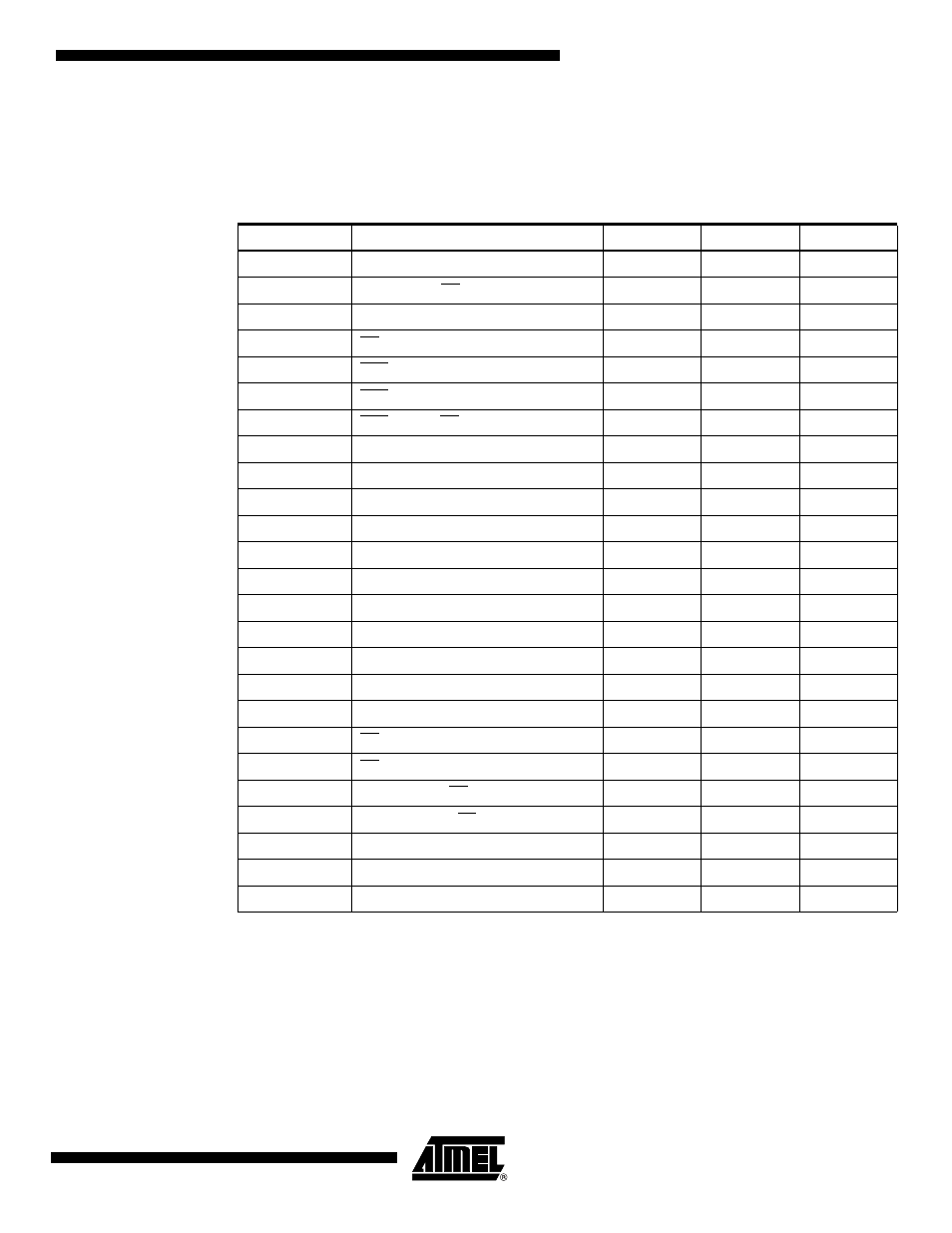

Table 23-6.

Programming Interface Timing Parameters

Symbol

Parameter

Min

Max

Units

t

CLCL

System Clock Cycle Time

0

60

ns

t

PWRUP

Power On to SS High Time

10

µs

t

POR

Power-on Reset Time

100

µs

t

PWRDN

SS Tristate to Power Off

1

µs

t

RLZ

RST Low to I/O Tristate

t

CLCL

2 t

CLCL

ns

t

STL

RST Low Settling Time

100

ns

t

RHZ

RST High to SS Tristate

0

2 t

CLCL

ns

t

SCK

Serial Clock Cycle Time

200

ns

t

SHSL

Clock High Time

75

ns

t

SLSH

Clock Low Time

50

ns

t

SR

Rise Time

25

ns

t

SF

Fall Time

25

ns

t

SIS

Serial Input Setup Time

10

ns

t

SIH

Serial Input Hold Time

10

ns

t

SOH

Serial Output Hold Time

10

ns

t

SOV

Serial Output Valid Time

35

ns

t

SOE

Output Enable Time

10

ns

t

SOX

Output Disable Time

25

ns

t

SSE

SS Enable Lead Time

t

SLSH

ns

t

SSD

SS Disable Lag Time

t

SLSH

ns

t

ZSS

SCK Setup to SS Low

25

ns

t

SSZ

SCK Hold after SS High

25

ns

t

WR

Write Cycle Time

2.5

ms

t

AWR

Write Cycle with Auto-Erase Time

5

ms

t

ERS

Chip Erase Cycle Time

7.5

ms