1 software reset – Rainbow Electronics AT89LP216 User Manual

Page 58

58

3621A–MICRO–6/06

AT89LP216 [Preliminary]

20.1

Software Reset

A Software Reset of the AT89LP216 is accomplished by writing the software reset sequence

5AH/A5H to the WDTRST SFR. The WDT does not need to be enabled to generate the software

reset. A normal software reset will set the SWRST flag in WDTCON. However, if at any time an

incorrect sequence is written to WDTRST (i.e. anything other than 1EH/E1H or 5AH/A5H), a

software reset will immediately be generated and both the SWRST and WDTOVF flags will be

set. In this manner an intentional software reset may be distinguished from a software error-gen-

erated reset. The program sequence to generate a software reset is as follows:

MOV WDTRST, #05Ah

MOV WDTRST, #0A5h

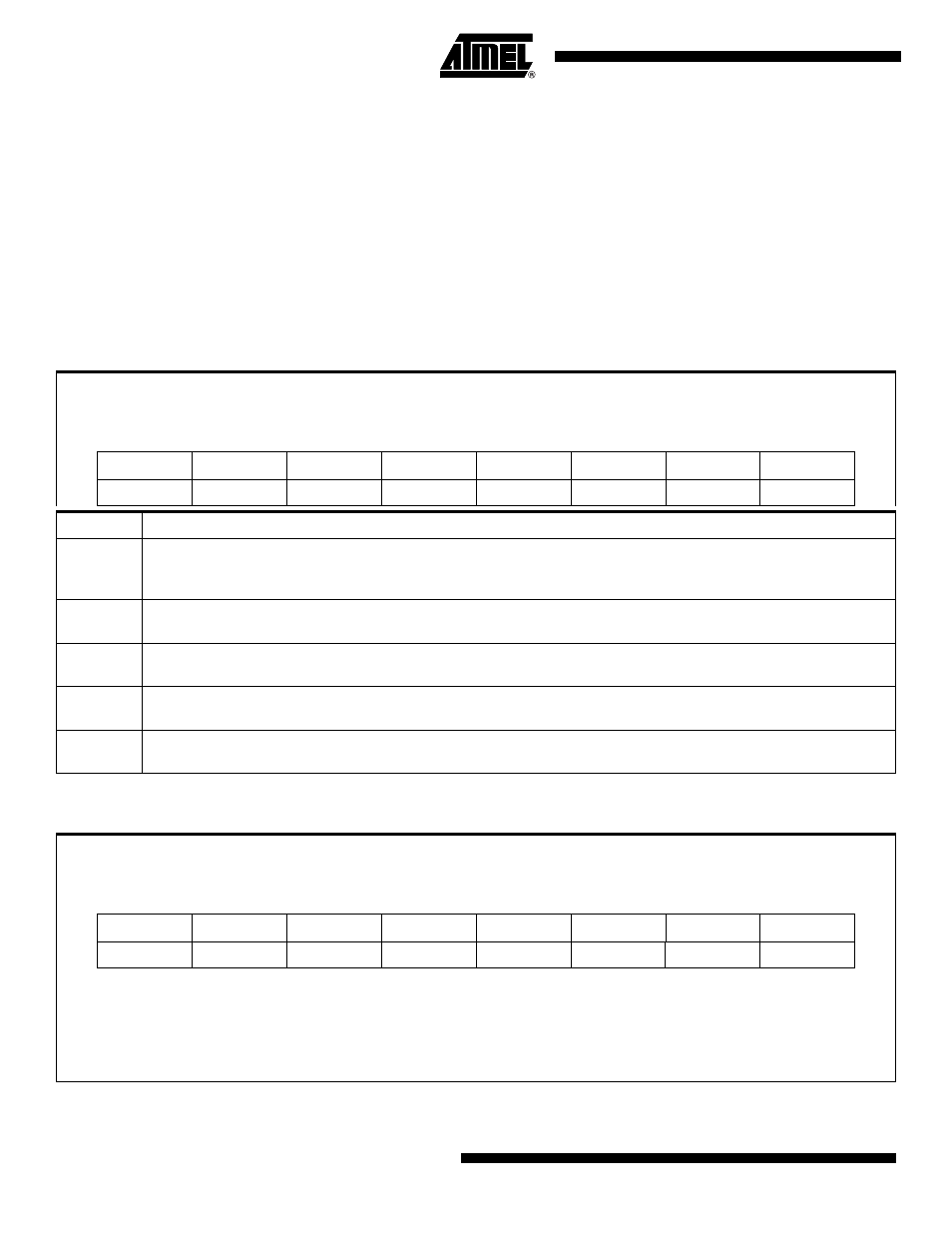

Table 20-2.

WDTCON – Watchdog Control Register

WDTCON Address = A7H

Reset Value = 0000 X000B

Not Bit Addressable

PS2

PS1

PS0

WDIDLE

–

SWRST

WDTOVF

WDTEN

Bit

7

6

5

4

3

2

1

0

Symbol

Function

PS2

PS1

PS0

Prescaler bits for the watchdog timer (WDT). When all three bits are cleared to 0, the watchdog timer has a nominal

period of 16K clock cycles. When all three bits are set to 1, the nominal period is 2048K clock cycles.

WDIDLE

Disable/enable the Watchdog Timer in IDLE mode. When WDIDLE = 0, WDT continues to count in IDLE mode. When

WDIDLE = 1, WDT freezes while the device is in IDLE mode.

SWRST

Software Reset Flag. Set when a software reset is generated by writing the sequence 5AH/A5H to WDTRST. Also set

when an incorrect sequence is written to WDTRST. Must be cleared by software.

WDTOVF

Watchdog Overflow Flag. Set when a WDT rest is generated by the WDT timer overflow. Also set when an incorrect

sequence is written to WDTRST. Must be cleared by software.

WDTEN

Watchdog Enable Flag. This bit is READ-ONLY and reflects the status of the WDT (whether it is running or not). The

WDT is disabled after any reset and must be re-enabled by writing 1EH/E1H to WDTRST

Table 20-3.

WDTRST – Watchdog Reset Register

WDTCON Address = A6H

(Write-Only)

Not Bit Addressable

–

–

–

–

–

–

–

–

Bit

7

6

5

4

3

2

1

0

The WDT is enabled by writing the sequence 1EH/E1H to the WDTRST SFR. The current status may be checked by reading

the WDTEN bit in WDTCON. To prevent the WDT from resetting the device, the same sequence 1EH/E1H must be written to

WDTRST before the time-out interval expires. A software reset is generated by writing the sequence 5AH/A5H to WDTRST.