Attiny28l/v – Rainbow Electronics ATtiny28L User Manual

Page 35

35

ATtiny28L/V

1062E–10/01

• Bit 2 – RES: Reserved Bit

This bit is a reserved bit in the ATtiny28 and will always read as zero.

• Bits 1, 0 - ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events trigger the Analog Comparator Interrupt.

The different settings are shown in Table 16.

Note:

When changing the ACIS1/ACIS0 bits, the Analog Comparator Interrupt must be dis-

abled by clearing its Interrupt Enable bit in the ACSR register. Otherwise, an interrupt can

occur when the bits are changed.

Caution: Using the SBI or CBI instruction on bits other than ACI in this register will write

a one back into ACI if it is read as set, thus clearing the flag.

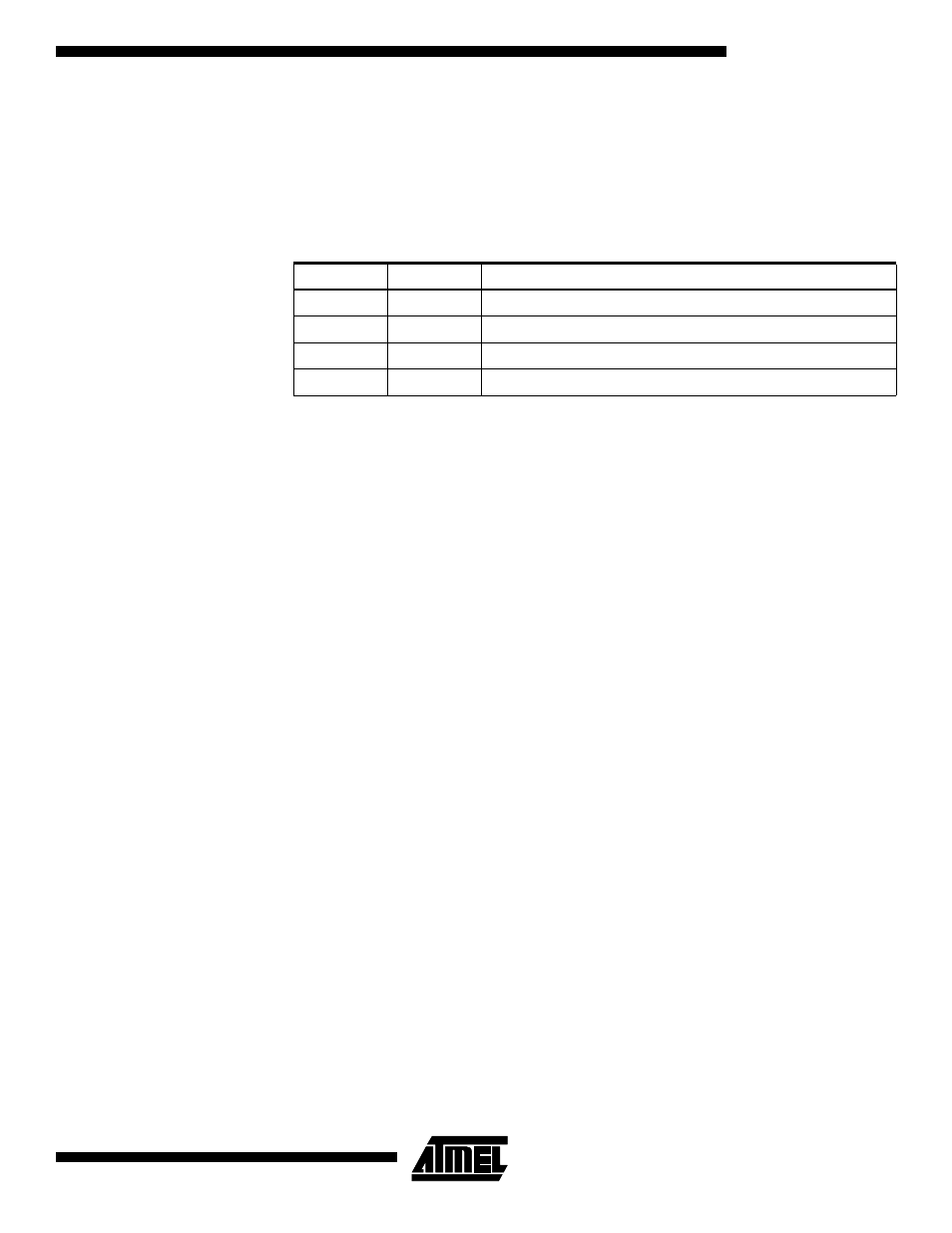

Table 16. ACIS1/ACIS0 Settings

ACIS1

ACIS0

Interrupt Mode

0

0

Comparator Interrupt on Output Toggle

0

1

Reserved

1

0

Comparator Interrupt on Falling Output Edge

1

1

Comparator Interrupt on Rising Output Edge

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)