Watchdog reset, Mcu control and status register – mcucs, Attiny28l/v – Rainbow Electronics ATtiny28L User Manual

Page 17

17

ATtiny28L/V

1062E–10/01

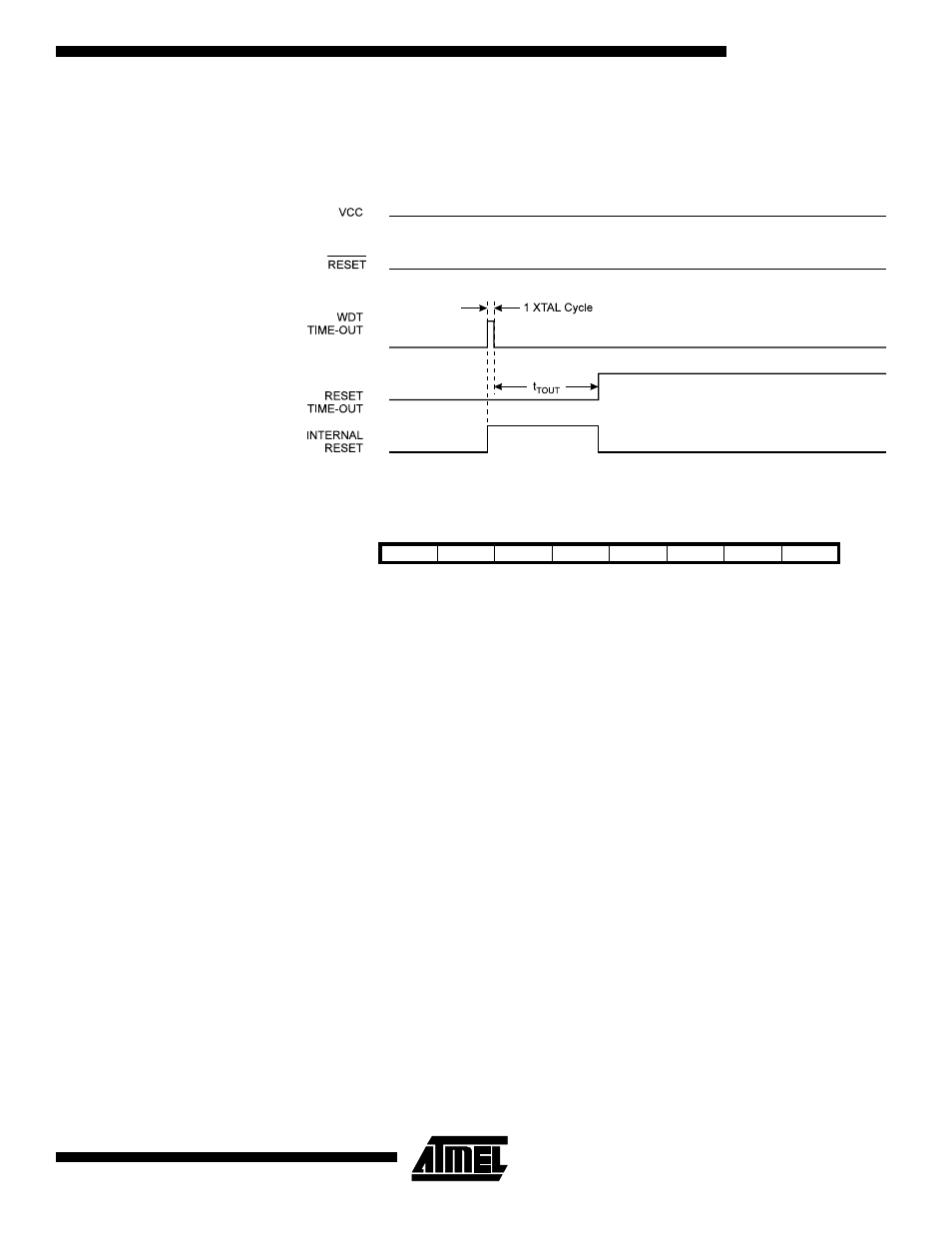

Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of 1 XTAL cycle dura-

tion. On the falling edge of this pulse, the delay timer starts counting the Time-out period

(t

TOUT

). Refer to page 26 for details on operation of the Watchdog.

Figure 19. Watchdog Reset during Operation

MCU Control and Status

Register – MCUCS

The MCU Control and Status Register contains control and status bits for general MCU

functions.

• Bit 7 – PLUPB: Pull-up Enable Port B

When the PLUPB bit is set (one), pull-up resistors are enabled on all Port B input pins.

When PLUPB is cleared, the pull-ups are disabled. If any of the special functions of Port

B is enabled, the corresponding pull-up(s) is disabled, independent of the value of

PLUPB.

• Bit 6 – Res: Reserved Bit

This bit is a reserved bit in the ATtiny28 and always reads as zero.

• Bit 5 – SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP

instruction is executed. To avoid the MCU entering the sleep mode unless it is the pro-

grammer’s purpose, it is recommended to set the Sleep Enable SE bit just before the

execution of the SLEEP instruction.

• Bit 4 – SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle

Mode is selected as sleep mode. When SM is set (one), Power-down mode is selected

as sleep mode. For details, refer to “Sleep Modes” below.

• Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog reset occurs. The bit is cleared by a Power-on Reset, or by

writing a logical “0” to the flag.

• Bit 2 – Res: Reserved Bit

This bit is a reserved bit in the ATtiny28 and always reads as zero.

Bit

7

6

5

4

3

2

1

0

$07

PLUPB

–

SE

SM

WDRF

–

EXTRF

PORF

MCUCS

Read/Write

R/W

R

R/W

R/W

R/W

R

R/W

R/W

Initial Value

0

0

0

0

See Bit

Desc.

0

See Bit Description