I/o memory, Status register – sreg, Attiny28l/v – Rainbow Electronics ATtiny28L User Manual

Page 11

11

ATtiny28L/V

1062E–10/01

I/O Memory

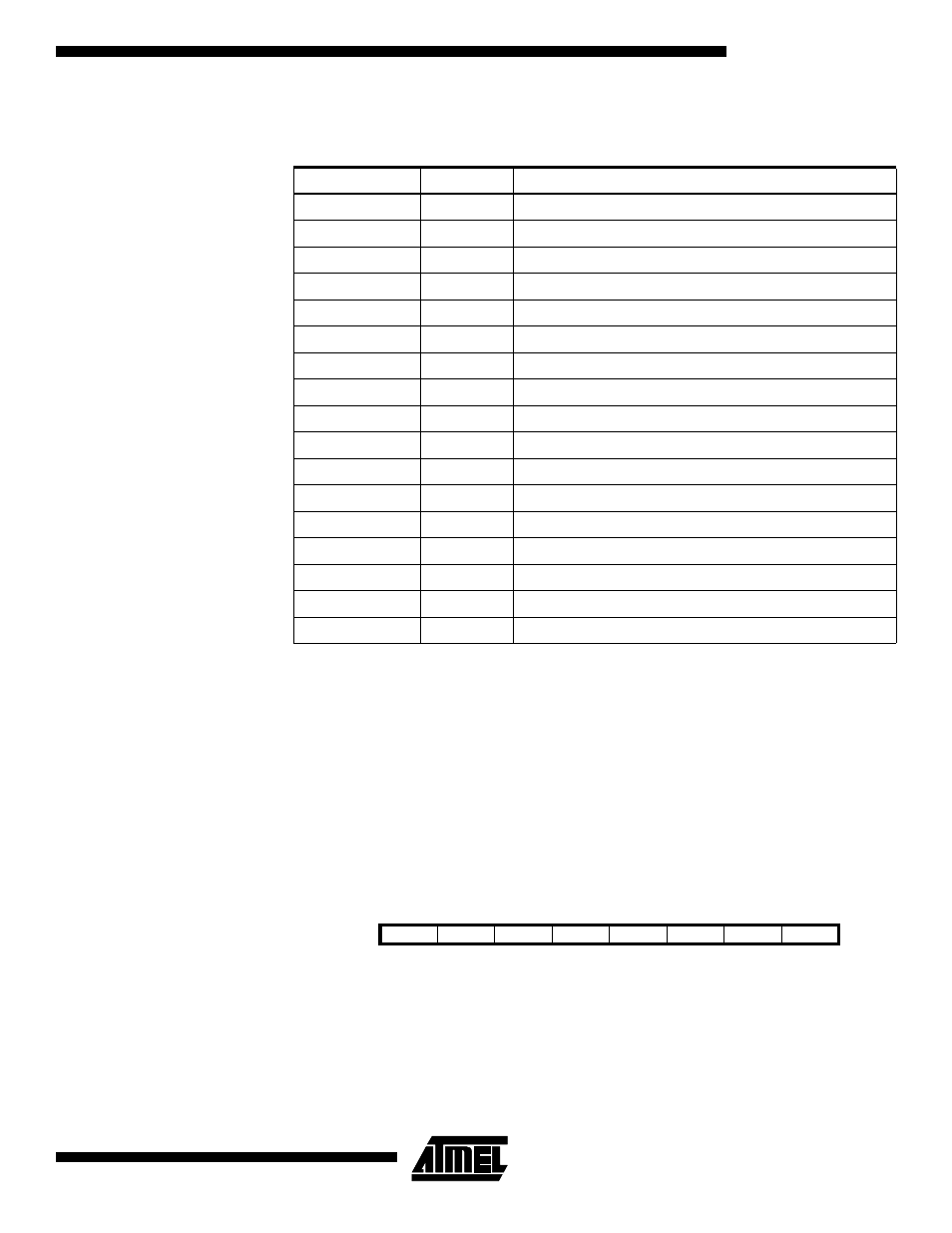

The I/O space definition of the ATtiny28 is shown in Table 2.

Note:

Reserved and unused locations are not shown in the table.

All ATtiny28 I/O and peripherals are placed in the I/O space. The I/O locations are

accessed by the IN and OUT instructions transferring data between the 32 general-pur-

pose working registers and the I/O space. I/O registers within the address range $00 -

$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the

value of single bits can be checked by using the SBIS and SBIC instructions. Refer to

the Instruction Set section for more details.

For compatibility with future devices, reserved bits should be written to zero if accessed.

Reserved I/O memory addresses should never be written.

The I/O and peripherals control registers are explained in the following sections.

Status Register – SREG

The AVR status register (SREG) at I/O space location $3F is defined as:

• Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The

individual interrupt enable control is then performed in separate control registers. If the

global interrupt enable register is cleared (zero), none of the interrupts are enabled inde-

pendent of the individual interrupt enable settings. The I-bit is cleared by hardware after

Table 2. ATtiny28 I/O Space

Address Hex

Name

Function

$3F

SREG

Status Register

$1B

PORTA

Data Register, Port A

$1A

PACR

Port A Control Register

$19

PINA

Input Pins, Port A

$16

PINB

Input Pins, Port B

$12

PORTD

Data Register, Port D

$11

DDRD

Data Direction Register, Port D

$10

PIND

Input Pins, Port D

$08

ACSR

Analog Comparator Control and Status Register

$07

MCUCS

MCU Control and Status Register

$06

ICR

Interrupt Control Register

$05

IFR

Interrupt Flag Register

$04

TCCR0

Timer/Counter0 Control Register

$03

TCNT0

Timer/Counter0 (8-bit)

$02

MODCR

Modulation Control Register

$01

WDTCR

Watchdog Timer Control Register

$00

OSCCAL

Oscillator Calibration Register

Bit

7

6

5

4

3

2

1

0

$3F

I

T

H

S

V

N

Z

C

SREG

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0