Pin description – Rainbow Electronics MAX9452 User Manual

Page 6

MAX9450/MAX9451/MAX9452

High-Precision Clock Generators

with Integrated VCXO

6

_______________________________________________________________________________________

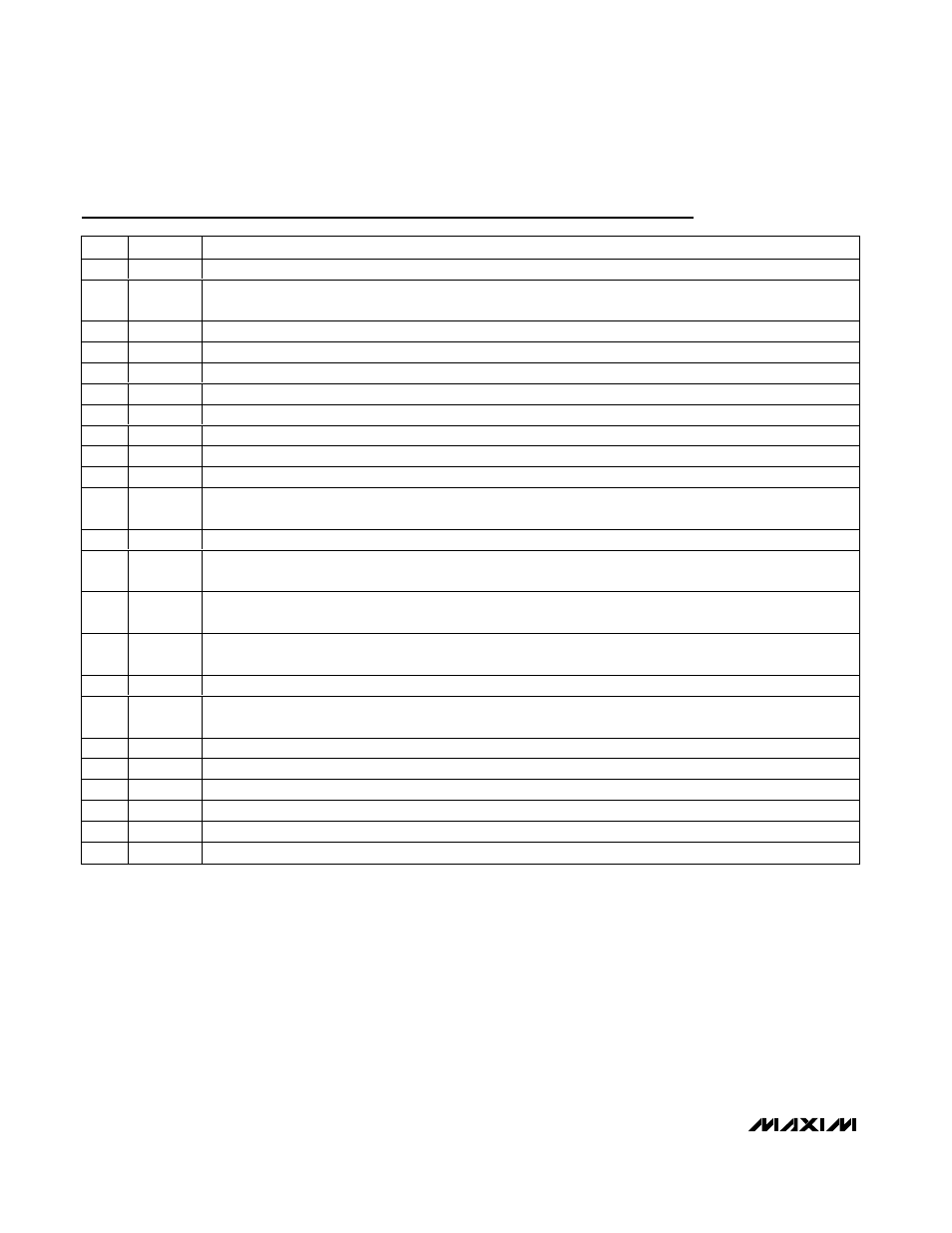

Pin Description

PIN

NAME

FUNCTION

1

LOCK

Lock Indicator.

LOCK goes low when the PLL locks. LOCK is high when the PLL is not locked.

2, 3

S E L0, S E L1

INO_ and IN1_ Select Inputs. Drive SEL0 high to activate IN0; drive SEL1 high to activate IN1. Driving SEL0 and

SEL1 low disables the corresponding input. A 165k

Ω pullup resistor pulls SEL0 and SEL1 up to V

DD

.

4, 5

IN0+, IN0-

Differential Reference Input Pair. IN0+ and IN0- accept LVPECL, LVDS, and LVCMOS signals.

6, 25

V

DD

Digital Power Supply. Connect a 2.4V to 3.6V power supply to V

DD

. Bypass V

DD

to GND with a 0.1µF capacitor.

7, 8

IN1+, IN1-

Differential Reference Input Pair. IN1+ and IN1- accept LVPECL, LVDS, and LVCMOS signals.

9

INT

Reference Input Condition Indicator. A high indicates a failed reference.

10

MR

Master Reset. Drive MR high to reset all I

2

C registers to their default state and INT to 0.

11

GND/

CS

Ground and Chip-Select Input. Connect to GND in I

2

C mode. This is the chip-select input in SPI mode.

12

SCL

Clock Input. SCL is the clock input in I

2

C bus mode and SPI bus mode.

13

SDA

Data Input. SDA is the data input in I

2

C bus mode and SPI bus mode.

14, 15

AD0, AD1

I

2

C Address Selection. Drive AD0 and AD1 high to convert the serial interface from I

2

C to SPI. GND/

CS

becomes

CS. See Table 3 for the unique addresses list.

16

CMON

Clock Monitor. Drive

CMON low to enable the clock monitor. Drive CMON high to disable the clock monitor.

17

OE

Output Enable Input. Drive

OE low to enable the clock outputs. Driving OE high disables the clock outputs, and

the outputs go high impedance. An internal 165k

Ω pullup resistor pulls OE up to V

DD

.

18, 24

V

DDQ

Clock-Output Power Supply. Connect a 2.4V to 3.6V power supply to V

DDQ

for the MAX9450 and MAX9452.

Connect a 1.5V power supply to V

DDQ

for the MAX9451. Connect a 0.1µF bypass capacitor from V

DDQ

to GND.

19, 20

CLK0-,

CLK0+

Differential Clock Output 0. The MAX9450 features LVPECL outputs. The MAX9451 features HSTL outputs and

the MAX9452 features LVDS outputs.

21

GND

Digital GND

22, 23

CLK1-,

CLK1+

Differential Clock Output 1. The MAX9450 features LVPECL outputs. The MAX9451 features HSTL outputs, and

the MAX9452 features LVDS outputs.

26, 27

X1, X2

Reference Crystal Input. Connect the reference crystal from X1 to X2.

28

V

DDA

Anal og P ow er S up p l y. C onnect a 2.4V to 3.6V p ow er sup p l y to V

D D A

. Byp ass V

D D A

to GN D A w i th a 0.1µF cap aci tor .

29, 30

LP1, LP2

External Loop Filter. Connect an RC circuit between LP1 and LP2. See the External Loop Filter section.

31

GNDA

Analog Ground

32

RJ

Charge-Pump Set Current. Connect an external resistor to GND to set the charge-pump current. See Table 11.

EP

EP

Exposed Pad. Connect to ground.