Table 3. i, C address setting by ad0 and ad1, Table 4. i – Rainbow Electronics MAX9452 User Manual

Page 13: C and spi register address, Table 5. dividing rate setting for p divider, Table 6. dividing rate setting for m divider

MAX9450/MAX9451/MAX9452

High-Precision Clock Generators

with Integrated VCXO

______________________________________________________________________________________

13

AD0

AD1

ADDRESS

Low

Low

1101000

Low

Open

1101001

Low

High

1101010

Open

Low

1101011

Open

Open

1101100

Open

High

1101101

High

Low

1101110

High

Open

1101111

High

High

Covert to SPI

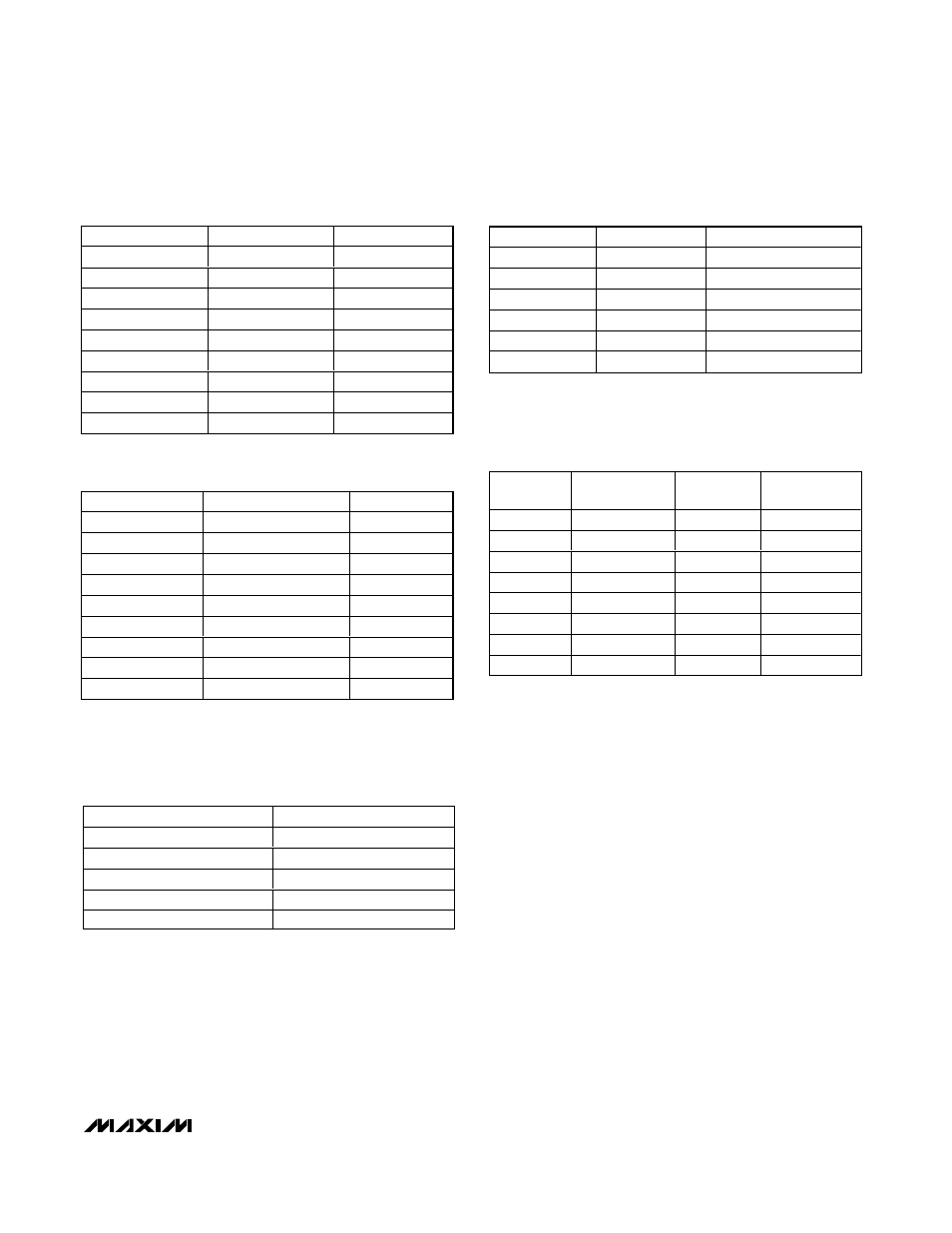

Table 3. I

2

C Address Setting by AD0 and AD1

REGISTER NAME

REGISTER ADDRESS

FUNCTION

CR0

00000000

P divider

CR1

00000001

M divider byte 1

CR2

00000010

M divider byte 2

CR3

00000011

N1 divider

CR4

00000100

N2 divider

CR5

00000101

Control

CR6

00000110

Control

CR7

00000111

Status

CR8

00001000

Reserved

Table 4. I

2

C and SPI Register Address*

CR0

DIVIDING RATE FOR P

0000-0000

1

0000-0001

2

—

—

1111-1110

255

1111-1111

256

Table 5. Dividing Rate Setting for P Divider

CR1

CR2[7:1]*

DIVIDING VALUE OF M

0000-0000

0000-000

1

0000-0000

0000-001

2

—

—

—

1111-1111

0011-110

8191

1111-1111

0011-111

8192

1111-1111

1111-111

32,768

Table 6. Dividing Rate Setting for M Divider

*When the SPI port is activated, the first address bit on the left

is omitted and the remaining seven bits are used. The LSB is

the first bit on the right.

*The last 5 LSBs of CR3[4:0] and CR4[4:0] are reserved.

*CR2[0], the last LSB, is reserved.

CR3*

DIVIDING

VALUE OF N0

CR4*

DIVIDING

VALUE OF N1

000XXXXX

1

000XXXXX

1

001XXXXX

2

001XXXXX

2

010XXXXX

3

010XXXXX

3

011XXXXX

4

011XXXXX

4

100XXXXX

5

100XXXXX

5

101XXXXX

6

101XXXXX

6

110XXXXX

8

110XXXXX

8

111XXXXX

16

111XXXXX

16

Table 7. Dividing Rate Setting for N0 and

N1 Divider