Rainbow Electronics MAX9452 User Manual

Page 10

MAX9450/MAX9451/MAX9452

High-Precision Clock Generators

with Integrated VCXO

10

______________________________________________________________________________________

External Loop Filter

When the device switches from one input reference to

the other or reverts to an input reference from holdover,

the output phase changes smoothly during the transition

using an external PLL filter. The narrower the filter band-

width is, the smoother the phase transition. However, if

bandwidth is too narrow, it can cause some degrada-

tion on output jitter performance.

Charge-Pump Current Setting

The MAX9450/MAX9451/MAX9452 allow external setting

of the charge-pump current in the PLL. Connect a resis-

tor from RJ to GNDA to set the PLL charge-pump current:

charge-pump current (µA) = 2.48 x 1000 /

(R

SET

(k

Ω) + 0.375)

where R

SET

is in k

Ω and the value of the charge-pump

current is in µA. Use R

SET

to adjust the loop response

to meet individual application requirements. The

charge-pump current and the external filter compo-

nents change the PLL bandwidth. Table 11 shows the

charge-pump current vs. the resistor’s value.

The loop response equation is defined as:

unity-gain bandwidth = (I

CP

x R

FILT

x 12kHz) / M

where I

CP

is the-charge pump current set by REXT,

R

FILT

is the external filter resistance, and M is the feed-

back divider.

Input Disable

The two inputs can be disabled separately by SEL0

and SEL1 or the two bits in CR5[3:2]. Table 2 shows the

state map.

Power-Up and Master Reset

Upon power-up, default frequency divider rates and the

states of the monitor, inputs, and outputs are set

according to Table 10. Setting MR high or CR6[4] to 1

also resets the device. When the device resets, INT

and CR7[5:6] go low and all the registers revert to their

default values.

I

2

C Interface

The control interface of the MAX9450/MAX9451/MAX9452

is an I

2

C or SPI depending on the states of AD0 and

AD1. Drive both AD0 and AD1 high to active SPI mode.

Otherwise, I

2

C is activated. The device operates as a

slave that sends and receives data through the clock

line, SCL, and data line, SDA, to achieve bidirectional

communication with the masters. A master (typically a

microcontroller) initiates all data transfers to and from

slaves, and generates the SCL clock that synchronizes

the data transfer. Figure 4 shows the timing of SCL and

SDA. The SDA line operates as both an input and an

open-drain output. SDA requires a pullup resistor, typi-

cally 4.7k

Ω. The SCL line operates only as an input. A

pullup resistor, typically 4.7k

Ω, is required on SCL if there

are multiple masters on the 2-wire bus, or if the master in

a single-master system has an open-drain SCL output.

I

2

C Device Address

Every I

2

C port has a 7-bit device address. This 7-bit

address is the slave (MAX9450/MAX9451/MAX9452)

ID for the master to write and read. In the MAX9450/

MAX9451/MAX9452, the first four bits (1101) of the

address are hard coded into the device at the factory.

See Table 3. The last three bits of the address are input

programmable by the three-level AD0 and AD1. This

configuration provides eight selectable addresses for

the MAX9450/MAX9451/MAX9452, allowing eight

devices to be connected to one master.

Start and Stop Conditions

Both SCL and SDA remain high when the interface is

not busy. The active master signals the beginning of a

transmission with a START (S) condition by transitioning

SDA from high to low while SCL is high. When the master

has finished communicating with the slave, it issues a

STOP (P) condition by transitioning SDA from low to

high while SCL is high. The bus is then free for another

transmission (Figure 3). The interval between a START

and a STOP is called a session.

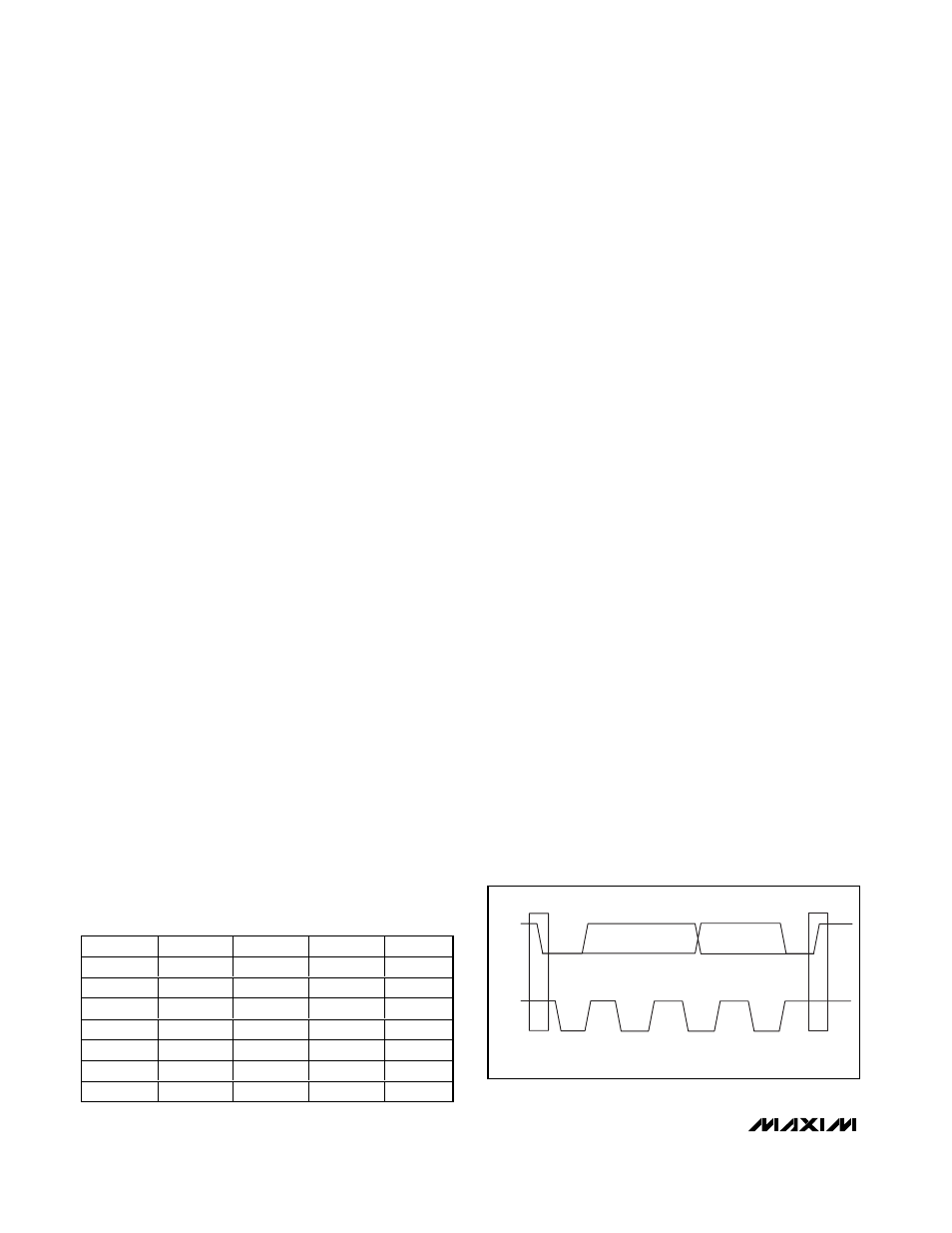

SEL1

SEL0

CR5[3:2]

IN1

IN0

0

0

00

Disabled

Disabled

0

1

00

Disabled

Enabled

1

0

00

Enabled

Disabled

1

1

00

Enabled

Enabled

X

X

01

Disabled

Enabled

X

X

10

Enabled

Disabled

X

X

11

Enabled

Enabled

Table 2. Input Activation by SEL0, SEL1,

or CR5[3:2]

SDA

SCL

S

START

CONDITION

P

STOP

CONDITION

Figure 3. Start and Stop Conditions