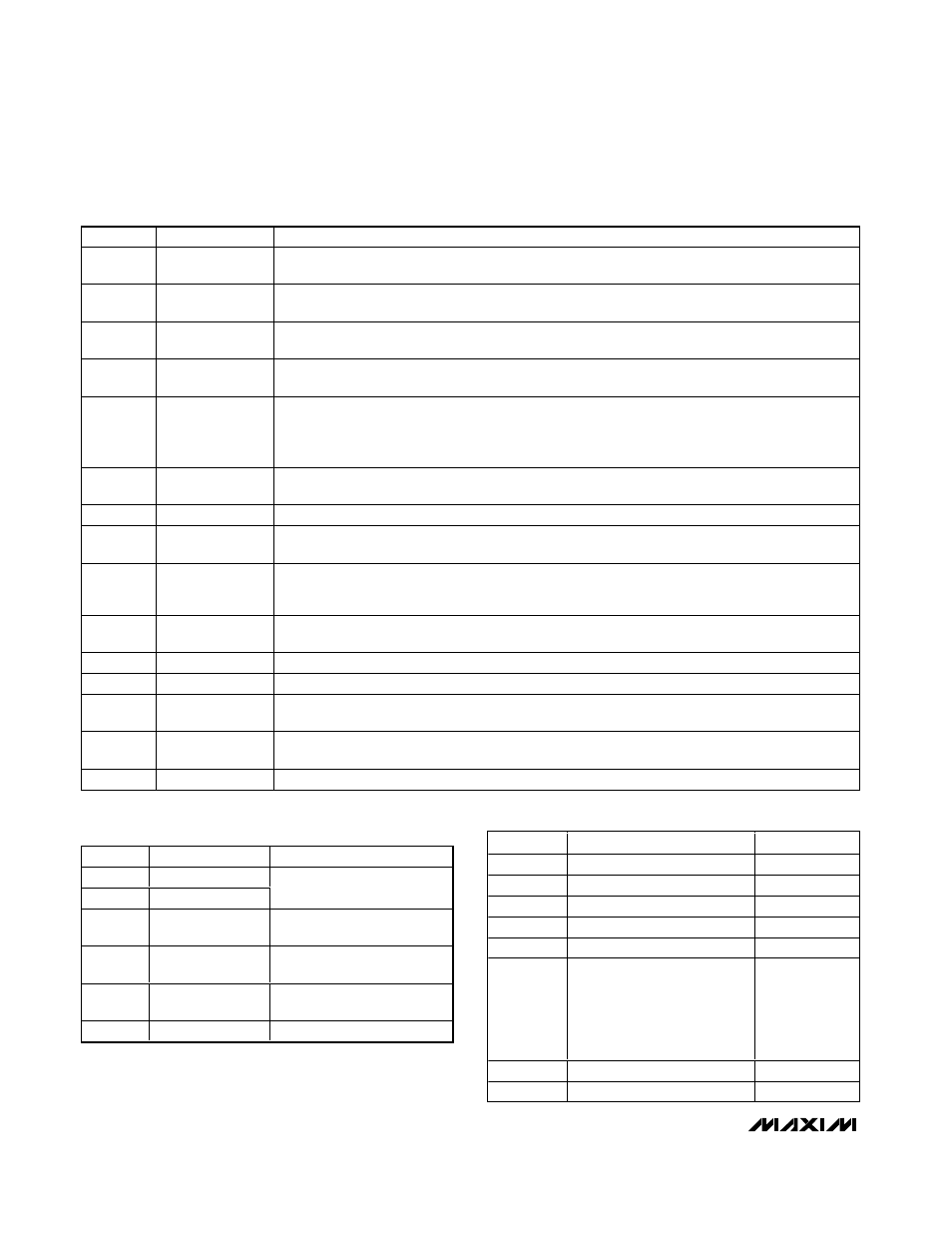

Table 10. register default values at power-up, Table 8. control registers and control functions, Table 9. mapping for the input monitor status – Rainbow Electronics MAX9452 User Manual

Page 14

MAX9450/MAX9451/MAX9452

High-Precision Clock Generators

with Integrated VCXO

14

______________________________________________________________________________________

REGISTER

ACTION

DEFAULT

CR0

P = 1

00000000

CR1

M = 1

00000000

CR2

M = 1

00000000

CR3

N0 = 1

00000000

CR4

N1 = 1

00000000

CR5, CR6

1. Outputs enable

2. IN0 is the default input

3. Both inputs are enabled by

SEL0 and SEL1

4. Monitor is nonrevertive

5. Holdover is disabled

CR5: 01100000

CR6: 00000000

CR7

Status

00000000

CR8

Reserved

00000000

Table 10. Register Default Values at Power-Up

CR5, CR6

FUNCTION

STATE

CR5[7]

Output disable

0: Outputs are enabled

1: Outputs disabled to logic-low

CR5[6]

CLK0 enabling

0: CLK0 is disabled to high impedance (overrides CR5[7] = 1 setting)

1: CLK0 is enabled

CR5[5]

CLK1 enabling

0: CLK1 is disabled to high impedance (overrides CR5[7] = 1 setting)

1: CLK1 is enabled

CR5[4]

Default input

setting

0: IN0 is the default input

1: IN1 is the default input

CR5[3:2]

Input enabling

00: The selection is controlled by SEL0, SEL1 (see Table 2)

01: Enable IN0, disable IN1

10: Enable IN1, disable IN0

11: Enable both IN0 and IN1

CR5[1]

Revert function

0: The function is not activated

1: The function is activated

CR5[0]

CLK monitor reset

C LK m oni tor i s r eset i n r ever t m od e: IN T = 0 and C R7[ 7] = 0, and the P LL sw i tches to the d efaul t i np ut

CR6[7]

Holdover function

enabling

0: Holdover function is disabled

1: Holdover function is enabled

CR6[6]

Forced holdover

0: Holdover is in normal mode

1: Holdover is forced to be activated

As the bit goes from 0 to 1, the current VCXO frequency is taken as the nominal value

CR6[5]

Acquiring nominal

VCXO frequency

As this bit is toggling from 0 to 1, the current VCXO frequency is taking as the nominal holdover

value

CR6[4]

Master reset

The bit acts at the same as the input MR; CR6[4] = 1, the chip is reset

CR6[3]

REF

This bit is always set to zero

CR6[2]

ODIV select

CR6[2] = 0: DIV0 output drives CLK2

CR6[2] = 1: DIV1 output drives CLK2

CR6[1]

Acquire select

CR6[1] = 0 PLL controls the Xtal frequency

CR6[1] = 1 Xtal frequency is controlled by the acquired value (acquired at rising edge of CR6[5])

CR6[0]

Reserved

—

Table 8. Control Registers and Control Functions

CR7

FUNCTION

STATE

CR7[6]

Status of IN0

CR7[5]

Status of IN1

0: Normal

1: Failure detected

CR7[4]

Input clock

selection indicator

0: IN0 is currently used

1: IN1 is currently used

CR7[3]

LOCK indicator

1: PLL not locked

0: PLL locked

CR7[2]

Holdover status

1: Device is in holdover state

0: Device is in normal state

CR7[1:0]

Reserved

—

Table 9. Mapping for the Input Monitor Status