Ac electrical characteristics (continued) – Rainbow Electronics MAX7032 User Manual

Page 5

MAX7032

Low-Cost, Crystal-Based, Programmable,

ASK/FSK Transceiver with Fractional-N PLL

_______________________________________________________________________________________

5

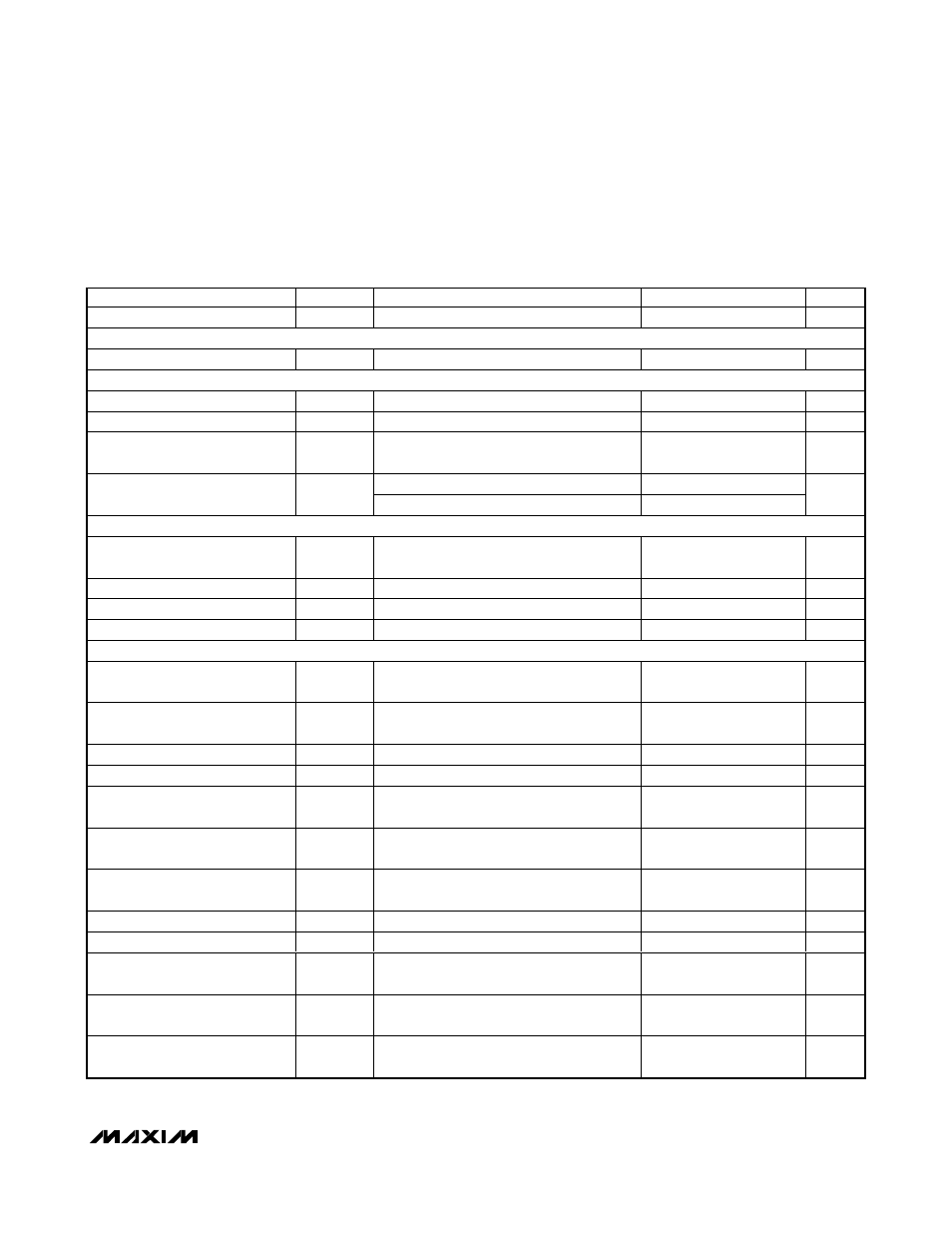

AC ELECTRICAL CHARACTERISTICS (continued)

(Typical Application Circuit, 50

Ω system impedance, AV

DD

= DV

DD

= PAV

DD

= HV

IN

= +2.1V to +3.6V, f

RF

= 300MHz to 450MHz, T

A

=

-40°C to +125°C, unless otherwise noted. Typical values are at PAV

DD

= AV

DD

= DV

DD

= HV

IN

= +2.7V, T

A

= +25°C, unless otherwise

noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Gain

15

mV/dB

FSK DEMODULATOR

Conversion Gain

2.0

mV/kHz

ANALOG BASEBAND

Maximum Data Filter Bandwidth

50

kHz

Maximum Data Slicer Bandwidth

100

kHz

Maximum Peak Detector

Bandwidth

50

kHz

Manchester coded

33

Maximum Data Rate

NRZ

66

kbps

CRYSTAL OSCILLATOR

Crystal Frequency

f

XTAL

(f

RF

- 10.7)

/ 24

MHz

Maximum Crystal Inductance

50

mH

Frequency Pulling by V

DD

2

ppm/V

Crystal Load Capacitance

(Note 7)

4.5

pF

SERIAL INTERFACE TIMING CHARACTERISTICS (see Figure 7)

Minimum SCLK Setup to Falling

Edge of CS

t

SC

30

ns

Minimum CS Falling Edge to

SCLK Rising-Edge Setup Time

t

CSS

30

ns

Minimum CS Idle Time

t

CSI

125

ns

Minimum CS Period

t

CS

2.125

µs

Maximum SCLK Falling Edge to

Data Valid Delay

t

DO

80

ns

Minimum Data Valid to SCLK

Rising-Edge Setup Time

t

DS

30

ns

Minimum Data Valid to SCLK

Rising-Edge Hold Time

t

DH

30

ns

Minimum SCLK High Pulse Width

t

CH

100

ns

Minimum SCLK Low Pulse Width

t

CL

100

ns

Minimum CS Rising Edge to

SCLK Rising-Edge Hold Time

t

CSH

30

ns

Maximum CS Falling Edge to

Output Enable Time

t

DV

25

ns

Maximum CS Rising Edge to

Output Disable Time

t

TR

25

ns