Detailed description – Rainbow Electronics MAX9491 User Manual

Page 6

MAX9491

Factory Programmable Single PLL

Clock Generator

6

_______________________________________________________________________________________

Detailed Description

The MAX9491 features a programmable fractional-N

PLL, so frequencies between 4MHz to 200MHz can be

generated. The device provides a buffered PLL clock

output. The crystal input frequency can be between

5MHz and 35MHz, and the clock input between 5MHz

and 50MHz. The internal VCXO has a fine-tuning range

of ±200ppm.

Power-Down

Driving

PD low places the MAX9491 in power-down

mode.

PD then sets CLK_OUT to high impedance and

shuts down the PLL. CLK_OUT has an 80k

Ω (typ) inter-

nal pulldown resistor.

Voltage-Controlled Crystal Oscillator

(VCXO)

The MAX9491’s internal VCXO produces a reference

clock for the PLL used to generate the CLK_OUT. The

oscillator uses a crystal as the base frequency refer-

ence and has a voltage-controlled tuning input for micro

adjustment in a ±200ppm range. The tuning voltage,

V

TUNE

, can vary from 0 to 3V as shown in Figure 1. The

crystal should be AT-cut and oscillate on its fundamen-

tal mode with ±30ppm. The crystal shunt capacitor

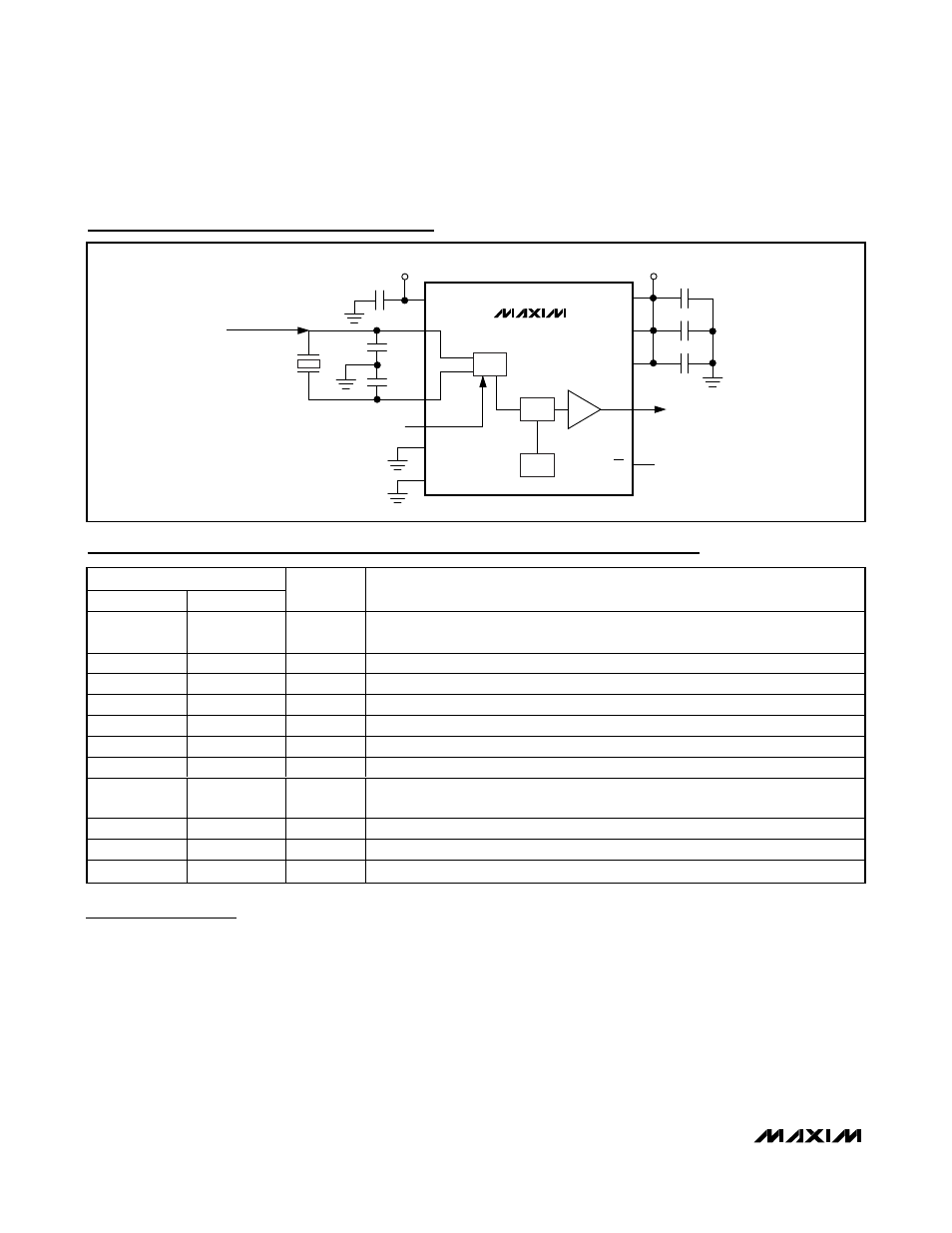

Pin Description

Typical Operating Circuit/Block Diagram

+3.3V

V

DD

V

DDA

V

DD

V

DD

0.1

µF x 3

0.1

µF

MAX9491

+3.3V

GND

AGND

TUNE

C1

C2

CLK_OUT

PLL

VCXO

X1

OR REFERENCE

INPUT

X2

OTP

PD

PIN

TQFN

TSSOP

NAME

FUNCTION

1

5

TUNE

VCXO Tune Voltage Input. If using a reference clock input or VCXO is not used,

connect TUNE to V

DD

.

2

—

V

DDA

Analog Power Supply. Bypass to GND with a 0.1µF capacitor.

3

—

AGND

Analog Ground

4, 10, 11

6, 9, 11

GND

Ground

5

7

CLK_OUT

Output Clock. Internally pulled down.

6–9, 14, 19, 20

2, 3, 8, 10

I.C.

Internally Connected. Leave unconnected for normal operation.

12, 13, 16

4, 12

V

DD

Power Supply. Bypass to GND with a 0.1µF capacitor.

15

13

PD

Active-Low Power-Down Input. Pull high for normal operation. Drive

PD low to place

MAX9491 in power-down mode. Internally pulled down.

17

14

X2

Crystal Connection 2. Leave unconnected if using a reference clock.

18

1

X1

Crystal Connection 1 or Reference Clock Input

EP

—

EP

Exposed Paddle (TQFN Only). Connect EP to GND or leave unconnected.