Rf12 – Rainbow Electronics RF12 User Manual

Page 18

RF12

Bits 2-0 (f2 to f0): DQD threshold parameter.

Note:

To let the DQD report "good signal quality" the threshold parameter should be less

than 4 in the case when the bit-rate is close to the deviation. At higher deviation/bit-rate

settings higher threshold parameter can report "good signal quality" as well.

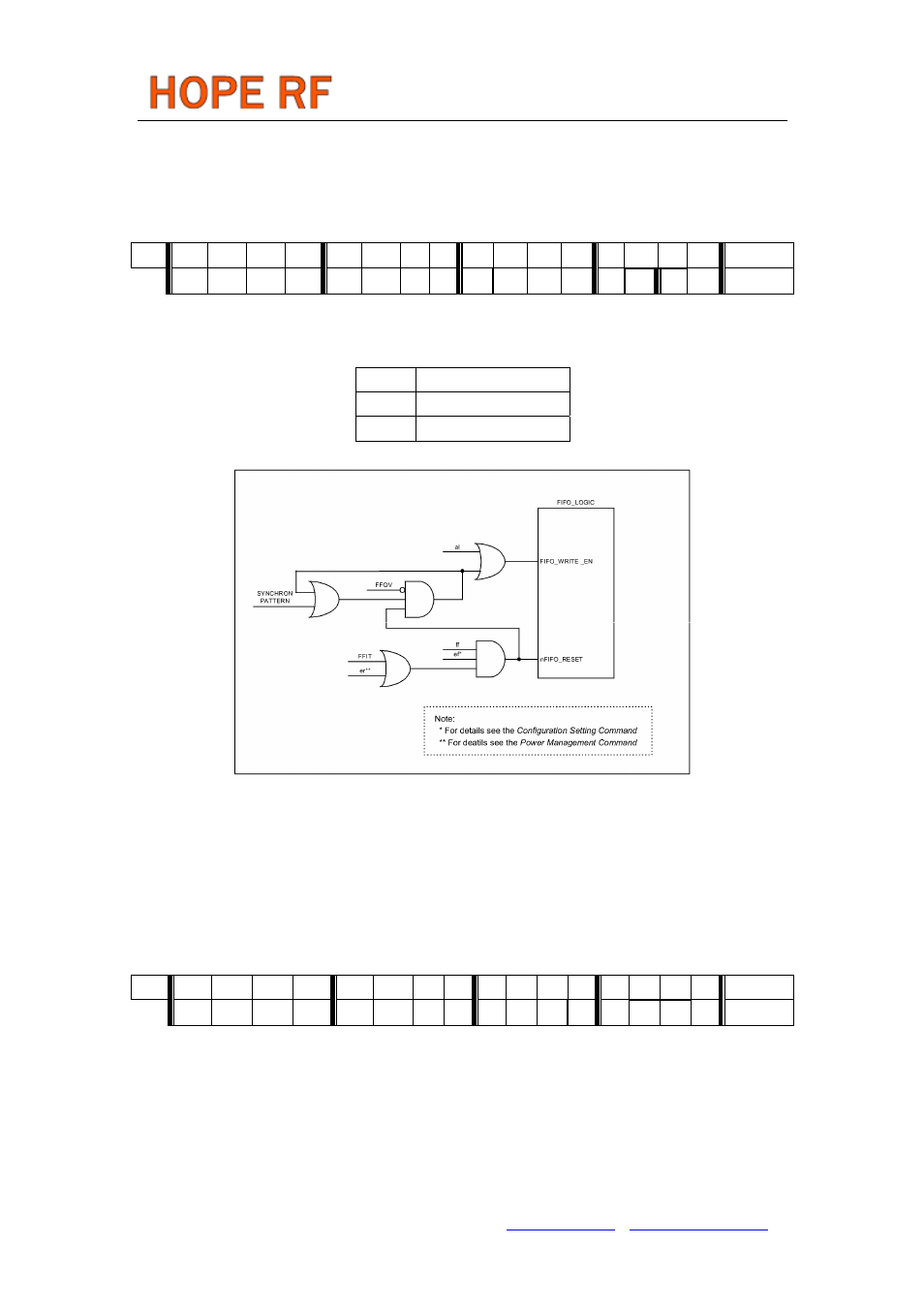

7. FIFO and Reset Mode Command

bit 15 14 13 12 11 10 9

8

7 6 5 4 3

2 1 0 POR

1 1 0 0 1 0 1

0

f3

f2

f1

f0

0

al

ff

dr

CA80h

Bits 7-4 (f4 to f0): FIFO IT level. The FIFO generates IT when the number of received data bits reaches

this level.

Bit 2 (al): Set the input of the FIFO fill start condition:

al

0

Synchron pattern

1

Always fill

Note:

Synchron pattern is 2DD4h.

Note:

For details see the Configuration Setting Command

For details see the Power Management Command

Bit 1 (ff): FIFO fill will be enabled after synchron pattern reception. The FIFO fill stops when this bit is

cleared.

Bit 0 (dr): Disables the highly sensitive RESET mode. If this bit is cleared, a 200 mV glitch in the power

supply may cause a system reset.

Note:

To restart the synchron pattern recognition, bit 1 should be cleared and set.

8. Receiver FIFO Read Command

bit 15 14 13 12 11 10 9 8

7 6 5 4

3 2 1 0 POR

1 0 1 1 0 0 0 0

0 0 0 0

0 0

0 0 B000h

With this command, the controller can read 8 bits from the receiver FIFO. Bit 6 (ef) must be set in

Configuration Setting Command.

Tel: +86-755-86096587 Fax: +86-755-86096602 E-mail: [email protected] http://www.hoperf.com