Toshiba TLP511E User Manual

Page 25

6-4

6-2-2. PLL IC TLC2932 (QX029) for Video Signal

The PLL IC of TLC2932 is composed of a phase

comparator and a VCO. As a frequency dividing circuit is

not built in, so the IC works as a PLL circuit by connect-

ing to the external VCO terminal of QX028 and using the

frequency dividing circuit of QX028.

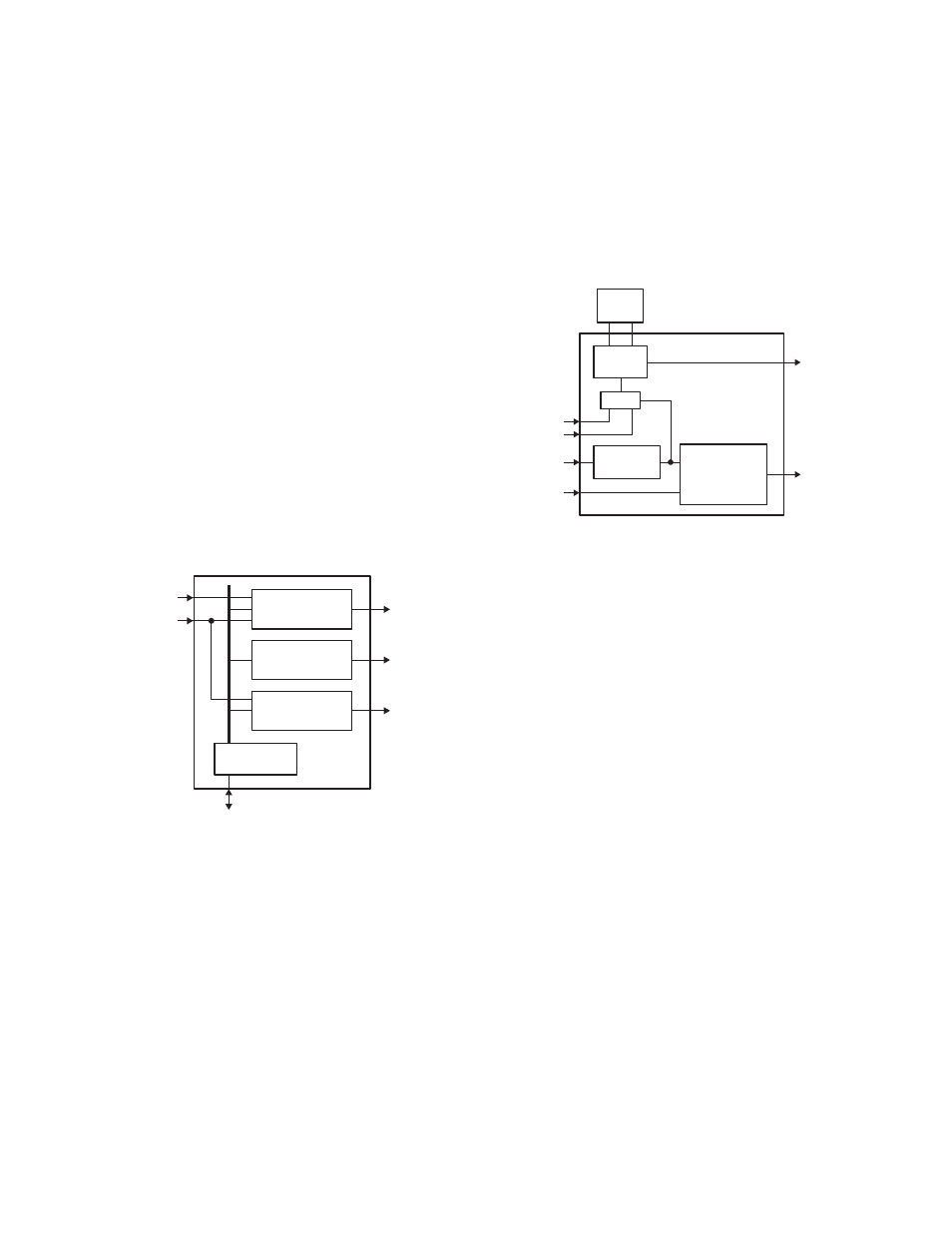

6-2-3. Sync Process IC SYG (QX004)

A configuration of the SYG component is shown in Fig.

6-2-2. The SYG IC is used as a sync process IC and

composed of the timing generation circuit for 2 systems,

one for the input signal and the other is for the panel

display, and the input signal measurement circuit. The IC

supplies the HD/VD signal to each IC and the IC works

on the timing signal basis. Also, the field identification at

video signal is carried out by the IC. In the unit, as the

PLL circuit is independent from the SYG, the sync signal

(DSYNC) enters from the PLL circuit to pin 139. The pin

is connected to the reset terminal of the horizontal

counter (for input signal).

Fig. 6-2-2

6-2-4. Timing Signal Generation PLD (QX009)

A configuration of timing signal generation PLD is

shown in Fig. 6-2-3. The timing generation PLD gener-

ates the clock pulse and the timing signal to drive the

panel. As the signal timing and clock differ owing to the

inverted driving for top/bottom/left/right of panel and

kinds of input signals, the mode signal controls the

timing signal generation PLD.

Fig. 6-2-3

6-2-5. A/D Converter CXA3026Q

(QX201, QX401 and QX601)

A configuration of CXA3026Q is shown in Fig. 6-2-4.

The max. conversion speed of 120 MHz is supported by

CXA3026Q, A/D converter.

A frequency dividing circuit is built in the A/D converter

and the converter develops the data for two systems. The

clock speed is fast, so that the clock signal to be entered

is a differential input of PECL level. The input level of

analog signal ranges from 2.0 to 4.0V.

MPU

SIGNAL FORMAT

MEASUREMENT

TIMING SIGNAL

GENERATOR 1

TIMING SIGNAL

GENERATOR 2

BUS

INTERFACE

32.5 MHz

HD, VD

PLL IC

QX008

PLL

CIRCUIT

SW

MODE

DECODER

PANEL TIMING

GENERATOR

Timing signals

for

LCD panel

PCLK

AD CLK/2

32.5 MHz

Mode

CLK, HD, VD