Reception process -4, 7. status read process -4 – Toshiba TLP511E User Manual

Page 15

5-4

5-3. Power Supply Reset Process

In the power supply reset process, power supply reset IC

(RN5VD27A), QL004 is employed.

The reset IC,QL004, develops the reset signal when the

power supply voltage for the microprocessor varies and

becomes lower than the specified voltage, and sends the

signal to the reset terminal of the system microprocessor

(QL002).

5-4. Non-volatile Memory Control Process

In the non-volatile memory process, data reading and

saving for various adjustments are carried out on the

non-volatile memory, QL006 (CAT24C16J).

When the power (AC) is on, all the adjustment data are

read out by the system microprocessor (QL002), then the

previous status is realized.

When saving the data, all the adjustment data are written

by the system microprocessor (QL002), then the current

status is preserved.

However, if a failure (such as power interruption due to

lightning, etc.) occurs during the adjustment data writing,

a data error may occur. If the data is determined as

incorrect, the initial data memorized on the system

microprocessor (QL002) is read out and stored on the

non-volatile memory.

5-5. Remote Control Reception Process

In the remote control reception process, a remote control

unit (CT-9925) connected to the remote control terminal

emits a remote control signal and a remote control signal

receive section on the front panel, the rear panel or the

camera arm (for TLP511) decodes the signal.

The remote control signals for rear panel and camera

section (for TLP511) are selected by QL012 buffer

(TC74HC125AF). Then both signals are mixed with the

remote control signal for front panel through QL005

buffer (74HC14AF).

Finally, the signal mixed is supplied to the remote control

terminal of the system microprocessor (QL002).

5-6. RS-232C Transmission/Reception

Process

In the RS-232C transmission/reception process, an RS-

232C signal entered through the RS-232C connector (D-

SUB 9P) is decoded in the RS-232C interface

(

m

PD4721), and fed to RXD1 terminal of the system

microprocessor (QL002).

In the RS-232C transmission process, RS-232C signal

developed from TXD0 terminal of the system micropro-

cessor (QL002) is decoded in the RS-232C interface

(

m

PD4721) and fed to the camera microprocessor

section.

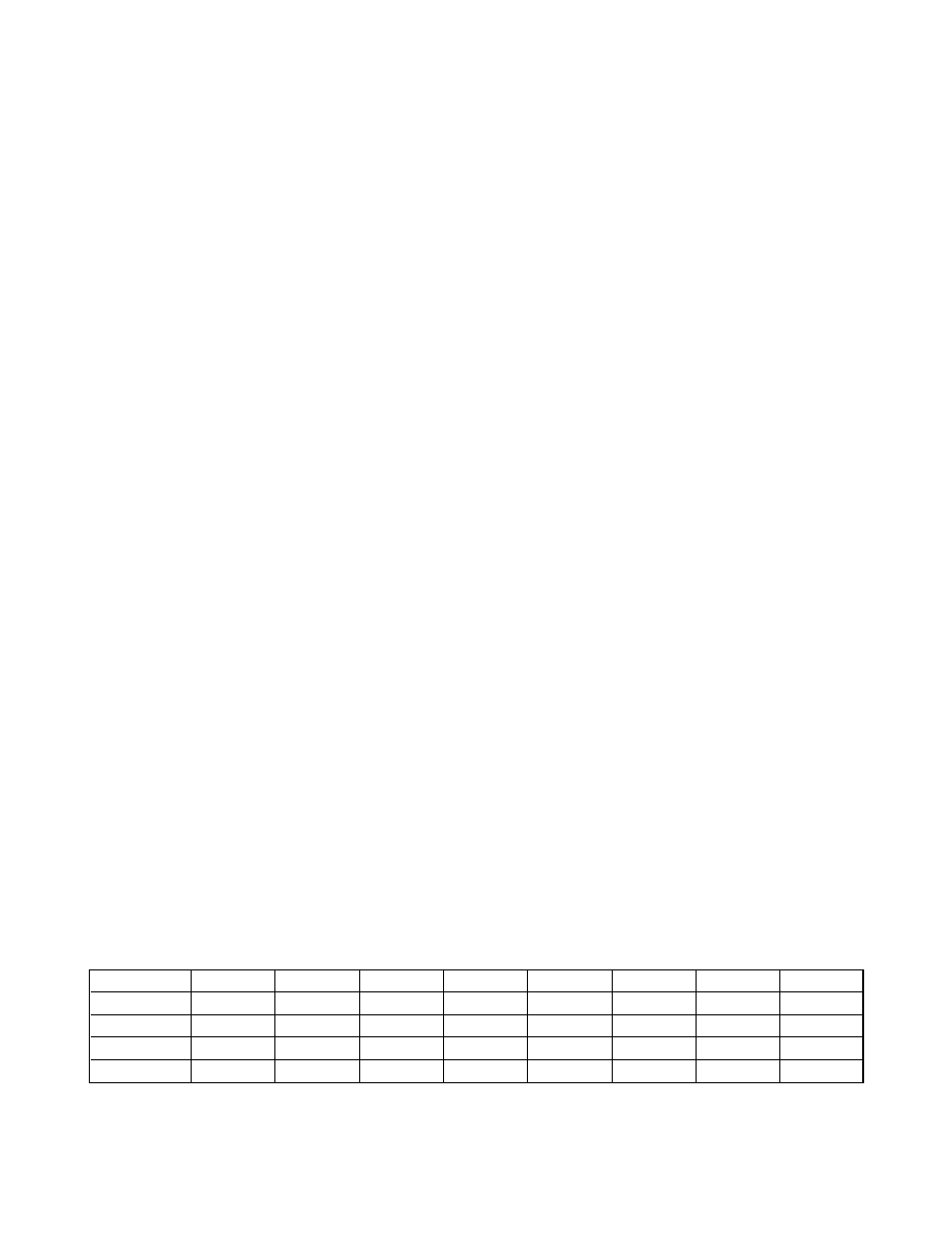

5-7. Status Read Process

In the status read process, the following status shown in

the table below are read by QL010 (74HC165AF) and

the error process corresponding to each status is carried

out.

Table 5-7-1 shows the contents of the status read signals

and the logic.

Signal name

Pin No.

QL010

(L)

(H)

A

11

FAN1. ER

Abnormal

Normal

B

12

FAN1. SW

Normal

Abnormal

C

13

FAN2. ER

Abnormal

Normal

D

14

E

3

TEMP1. ER

Normal

Abnormal

F

4

G

5

LAMP. ER

Abnormal

Normal

H

6

MAIN. ER

Abnormal

Normal

Table 5-7-1 The contents of the status read signals and the logic