Nortel Networks OPTera Metro 3500 User Manual

Page 25

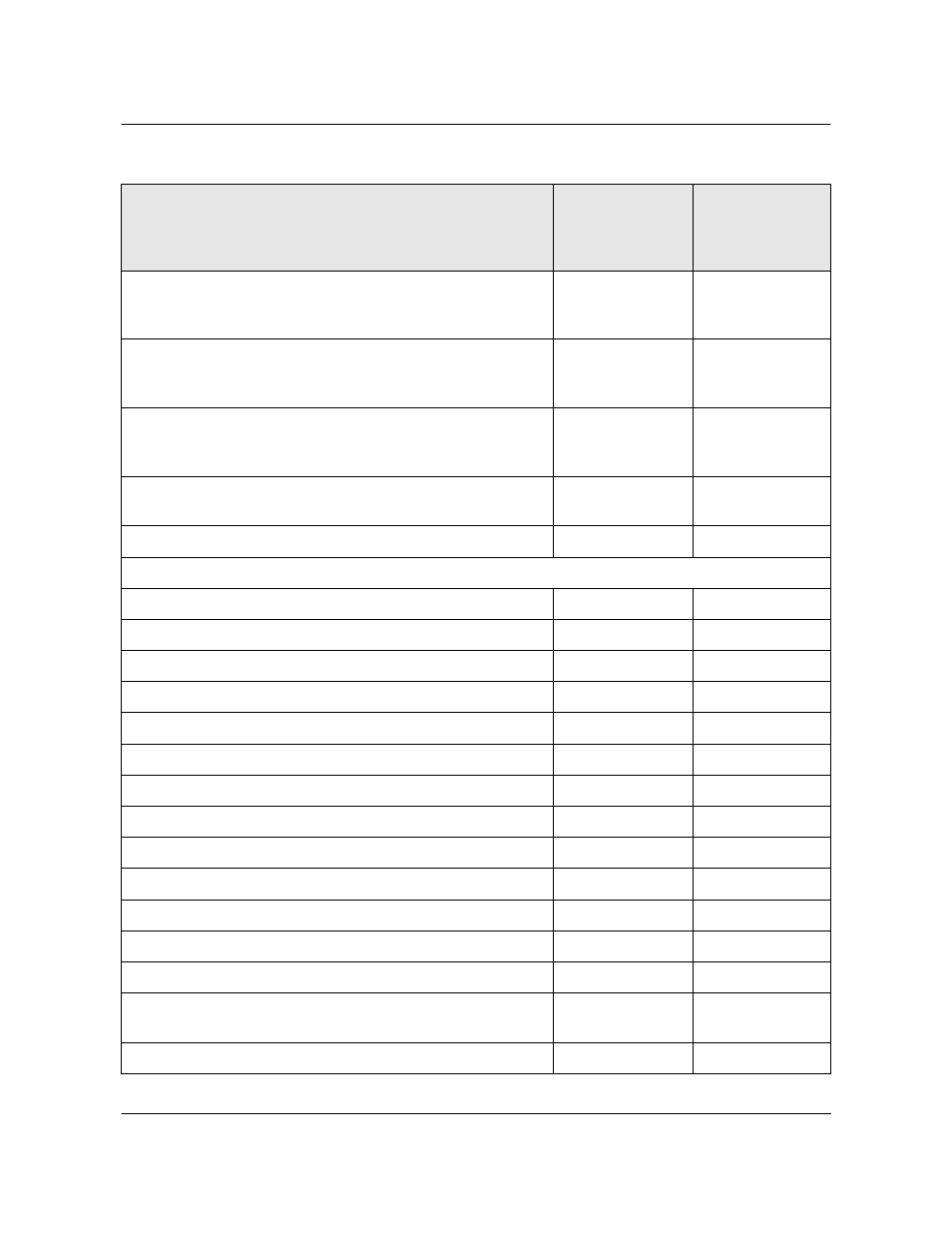

Overview 1-13

Planning and Ordering Guide—Part 1 of 2 NTRN10AN Rel 12.1 Standard Iss 1 Apr 2004

STS-48c, STS-24c, STS-12c, STS-3c, STS-1, VT1.5 time slot

interchange (TSI) on 1+1 linear, UPSR

Yes

except STS24c &

STS-48c

Yes

VT1.5

STS-48c, STS-24c, STS-12c, STS-3c, STS-1, VT1.5 time slot

interchange (TSI) on BLSR

Yes

except STS24c &

STS-48c

Yes

VT1.5

TU11, TU21, AU32, AU4 cross-connects (in J-SDH mode)

Yes

Yes

supports AU32

and AU4

VT1.5/ time slot assignment (TSA) on pass-through nodes on

BLSR

Yes

No

VT6 cross-connects (in J-SDH mode)

Yes

No

Miscellaneous

6.312-MHz clock (in J-SDH mode)

Yes

Yes

Alarm provisioning

Yes

Yes

Composite clock timing (in J-SDH mode)

Yes

Yes

Consolidated load

Yes

Yes

DS1 ESF BITS synchronization status messaging

Yes

Yes

DS1 automatic in-service (AINS)

Yes

Yes

DS1 loopback

Yes

No

DS3 automatic in-service (AINS) on T3 facilities

Yes

Yes

DS3 loopback

Yes

Yes

DS3/VT automatic in-service (AINS) on T3 facilities

Yes

No

External building-integrated timing supply (BITS) input/output

Yes

Yes

Full TARP

Yes

Yes

Hitless timing reference switching

Yes

Yes

Independent synchronization and bandwidth management

switching

Yes

Yes

Mixed tributaries

Yes

Yes

Table 1-1 (continued)

Feature compatibility for Release 12.1

Feature

Supported on

platforms with

VTX-series

circuit packs

Supported on

platforms with

STX circuit packs