Hierarchy violations, Timing loops, Hierarchy violations 2-151 timing loops 2-151 – Nortel Networks OPTera Metro 3500 User Manual

Page 189

Operation, administration, and maintenance (OAM) features 2-151

Planning and Ordering Guide—Part 1 of 2 NTRN10AN Rel 12.1 Standard Iss 1 Apr 2004

timing signal quality from a network element in holdover mode in the event a

timing reference is disrupted. See

Synchronization-status messages on page

.

Hierarchy violations

A hierarchy violation occurs when a clock of one stratum level is used to

synchronize a clock of a higher stratum level. A stratum 3 clock synchronizing

a stratum 2 clock is one such example. The synchronization network must be

carefully planned so that no hierarchy violations occur.

Timing loops

A timing loop is created when a clock is synchronizing itself, either directly or

through intermediate equipment. A timing loop causes excessive jitter and can

result in traffic loss.

Timing loops can be caused by a hierarchy violation, or by having clocks of

the same stratum level synchronize each other. In a digital network, timing

loops can be caused during the failure of a primary reference source, if the

secondary reference source is configured to receive timing from a derived

transport signal within the network.

A timing loop can also be caused by incorrectly provisioned synchronization

status message (SSM) for some of the facilities in a linear or ring system.

Under normal conditions, if there is a problem in the system (for example,

pulled fiber), the SSM functionality will heal the timing in the system.

However, if the SSM is incorrectly provisioned, the system might not be able

to heal itself and might segment part of itself in a timing loop.

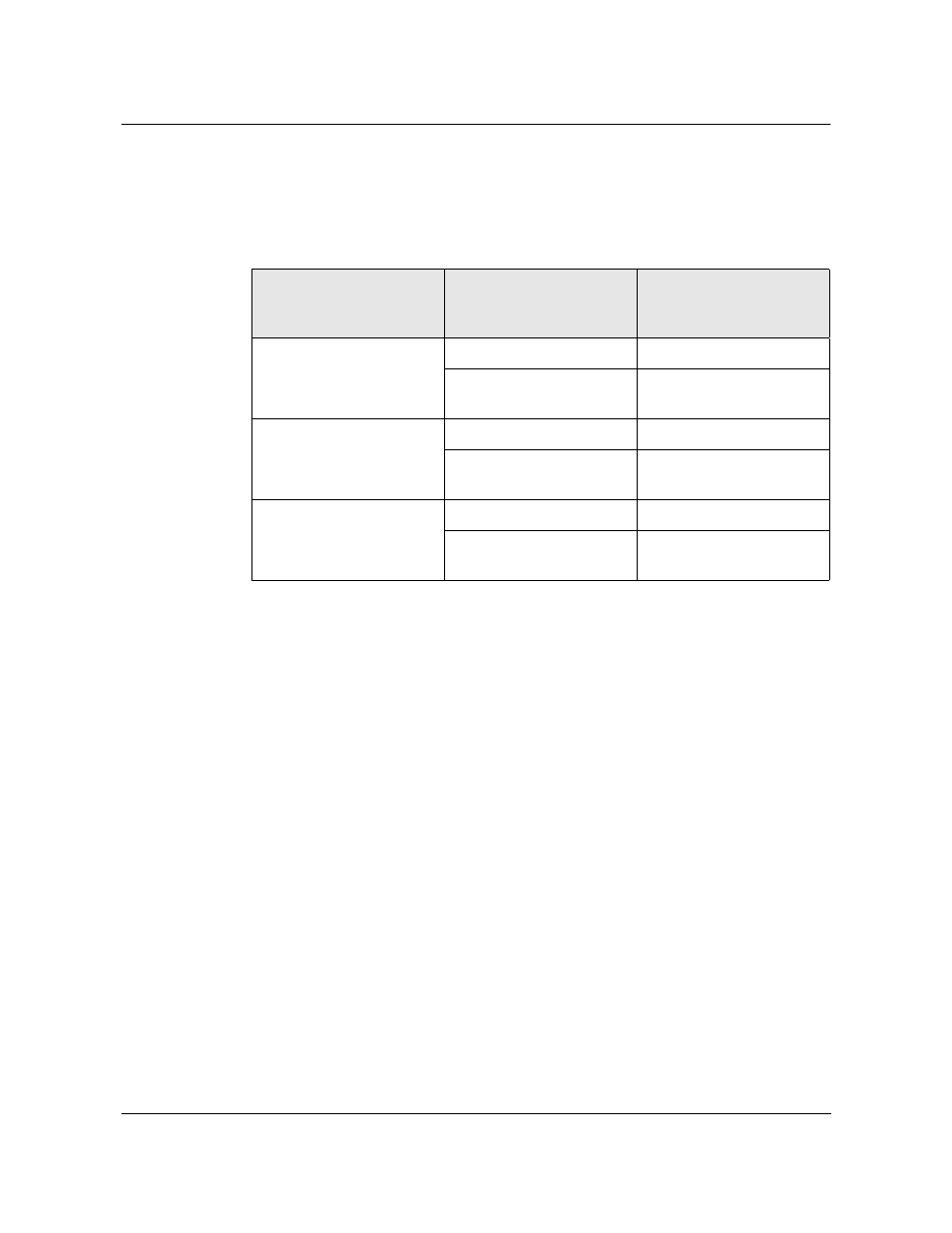

Table 2-32

Transmitted timing signal quality in holdover mode

Module

Quality of disrupted

timing reference

Quality of transmitted

timing signal in holdover

mode

VTX-48

≥ ST3

ST3

< ST3

(NE ignores signal)

ST3

VTX-48e

≥ ST3

ST3

< ST3

(NE ignores signal)

ST3

STX-192

≥ ST3

ST3

< ST3

(NE ignores signal)

ST3